반도체 10나노대 시대가 본격화하면서 쿼드러플 패터닝 기술(QPT)이 점차 중요해지고 있다.

과거 QPT는 기존 더블 패터닝(DPT)에서 극자외선(EUV)으로 전환되는 사이 징검다리 기술로만 인식됐다. 그러나 EUV 노광기 개발이 지연되면서 효율적인 QPT 공정을 확보한 업체가 10나노(㎚)대 반도체 시장을 주도할 것으로 예상된다.

26일 업계에 따르면 낸드 플래시와 시스템 반도체 미세 공정이 20나노대에서 최근 14~16나노로 전환되면서 QPT가 빠른 속도로 확산되고 있다. 기존 노광 기술인 DPT로는 물리적으로 19나노 미세회로가 한계기 때문이다.

인텔·삼성전자·TSMC 등 글로벌 업체는 시스템 반도체에 14~16나노 핀펫(FinFET) 기술을 적용하면서 QPT 노광 공정을 채택했다. 내년 초 출시될 차세대 애플리케이션 프로세서(AP)·중앙처리장치(CPU)에는 QPT 공정이 본격 적용된다.

낸드 플래시에도 QPT 공정이 도입되고 있다. SK하이닉스는 최근 낸드 플래시 미세 공정을 19나노에서 16나노로 전환하면서 QPT 공정을 쓰고 있다. 도시바도 15나노 미세 회로를 적용한 낸드 플래시를 개발하고 있어 조만간 QPT 공정을 채택할 것으로 예상된다.

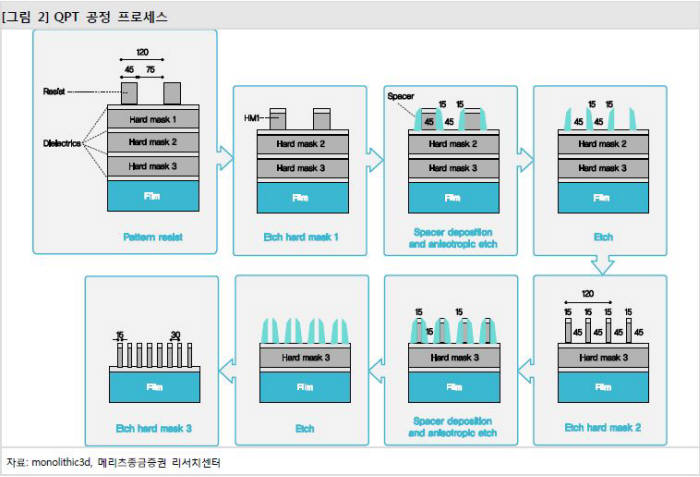

QPT는 기존 DPT 공정을 반복하는 방식으로 10나노대 미세 회로를 구현한 기술이다. DPT로 첫 번째 회로를 형성하고, 회로 사이에 또 하나의 패턴을 새겨 넣는 원리다. 기존 액침 노광기를 그대로 쓸 수 있고, DPT와 연속성도 커 안정적이다.

이론적으로는 QPT로 10나노 초반까지 가능하다. 그러나 반도체 업체들은 생산 난이도를 감안해 14~16나노까지만 상업화를 추진 중이다. QPT 공정이 고도화되면 향후 10~11나노 미세회로도 구현할 수 있다. 장기적으로 10나노 이하 미세공정에는 EUV 노광기가 쓰일 것으로 예상된다.

QPT 공정 중 회로 사이에 새로운 패턴을 형성하는 단계에서 희생막이 필요하다. 증착(CVD)·에칭(Etching)·화학기계적연마(CMP) 공정이 두 배 이상 늘어난다. 여기에서 반도체 업체 간 경쟁력이 판가름난다. 공정 효율화와 수율에 따라 생산 원가 차이가 발생하기 때문이다.

선두 업체들은 지난해부터 QPT 기술 효율화에 집중 투자하고 있다. 지난해까지만 해도 QPT는 DPT 공정 대비 70% 이상 생산비가 비쌌다. 그러나 최근 삼성전자 등 선두 업체들은 QPT 공정 비용을 DPT 대비 15~30% 수준까지 줄인 것으로 알려졌다.

업계 관계자는 “반도체 공정에 QPT가 적용되면 금속뿐 아니라 가스 등 다양한 소재가 첨가된다”며 “업체마다 공정이 다른 만큼 수율에도 결정적인 차이가 있을 것”이라고 말했다.

이형수기자 goldlion2@etnews.com