기존 극자외선(EUV) 노광기로도 3나노 '싱글 패터닝'을 구현할 수 있는 반도체 공정 기술이 개발됐다. 싱글 패터닝은 노광기에서 웨이퍼 위에 반도체 회로 모양을 한 번에 찍어내는 것을 말한다. 여러 번 회로를 찍는 '멀티 패터닝'을 할 때보다 생산 비용이 크게 줄어든다.

당초 반도체 업계는 3나노 EUV 싱글 패터닝이 차세대 '하이(High)-NA' 노광기에서만 가능할 것으로 예상했다. 하지만 ASML과 IMEC이 공동 연구개발을 통해 기술 구현을 앞당겼다. 삼성전자 등 반도체 제조사들은 장비 투자비용을 절감할 수 있을 것으로 기대된다.

2일 벨기에 반도체 연구 허브 IMEC은 ASML의 1세대 EUV 노광기 'NXE:3400B'로 3나노 싱글 패터닝 기술을 구현했다고 밝혔다. IMEC은 지난달 말 미국 새너제이에서 열린 세계적인 광학회 'SPIE'의 첨단 리소그래피 학회에서도 기술을 소개했다.

노광 공정은 반도체 제조 핵심 기술이다. 빛으로 웨이퍼 위에 반도체 회로를 반복적으로 찍어내는 작업이다. 기존에는 불화아르곤(ArF) 광원으로 노광 공정을 했지만, 반도체 초미세화로 기존보다 파장이 14분의 1가량 짧은 극자외선(EUV)을 활용한 공정이 빠르게 도입되고 있다.

EUV 노광 장비는 네덜란드 반도체 장비 기업 ASML이 독점 공급한다. 현재 삼성전자 등 반도체 제조사에 1세대 EUV 장비 NXE:3400B가 공급됐다.

노광 공정에서는 패터닝 횟수가 중요하다. 빛으로 원하는 회로를 단 한 번에 찍어내는 싱글 패터닝도 있지만, 미세 회로 공정이 필요할 때는 두 번(멀티플), 네 번(쿼드러플)씩 찍어내는 방법도 있다. 마치 벤다이어그램의 교집합처럼 여러 번 찍어내서 겹치는 얇은 부분을 회로로 쓴다.

하지만 여러 번 패터닝을 하면 싱글 패터닝을 할 때보다 비용이 훨씬 많이 든다. 노광 시스템 운용뿐 아니라 포토레지스트 코팅 등 다양한 준비를 거쳐야 하기 때문이다. 반도체 제조사들이 싱글 패터닝을 선호하는 이유다.

반도체 업계에서는 ASML 1세대 EUV 노광기로 7나노, 5나노 공정에서만 싱글 패터닝을 구현할 수 있는 것으로 알려졌다. 본격적인 3나노 기술은 렌즈 크기를 늘린 0.55NA 이상 차세대 High-NA 장비에서 구현할 것으로 예상됐다.

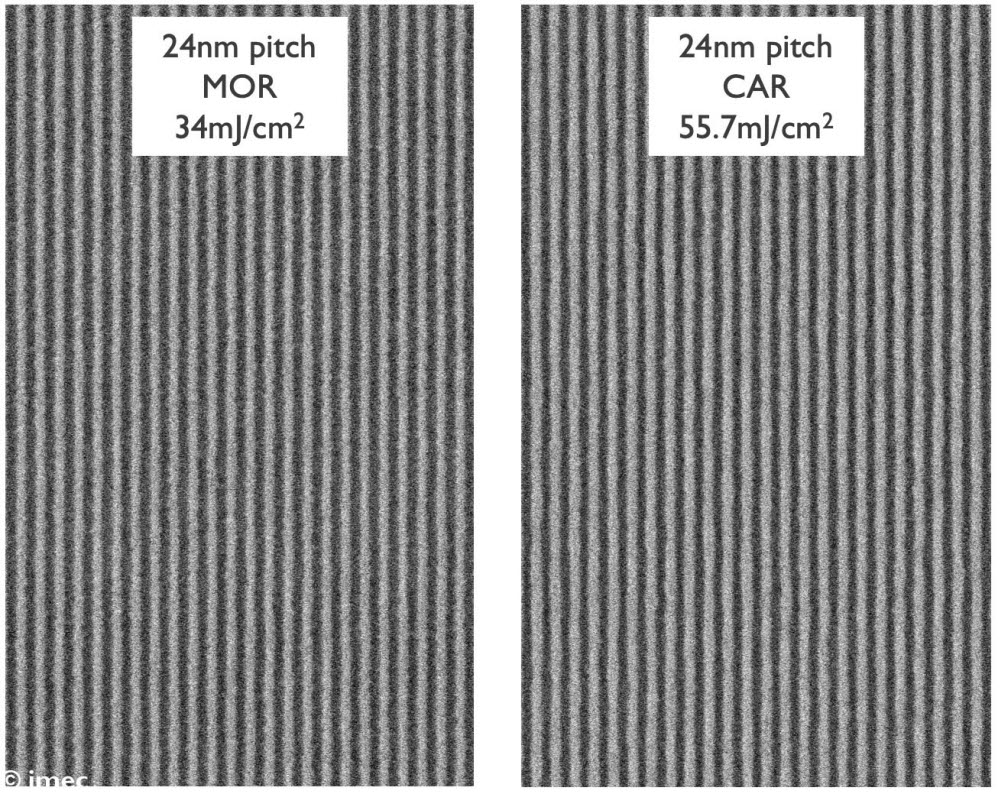

그러나 ASML과 IMEC은 EUV 광원의 입사각을 조율하면서 기존 장비로도 3나노 공정을 활용한 24㎚ 길이 피치 라인을 한 번에 찍어냈다.

IMEC 측은 “EUV 광원의 입사각이 높아 회로 모양이 그려진 마스크를 통과하면서 왜곡된 회로 이미지가 생기게 된다”며 “이 각도를 최적화해서 이미지 왜곡을 최소화하는 방안을 찾아냈다”고 밝혔다.

이 기술이 상용화되면 EUV 공정 도입을 가속화하는 반도체 업계에 큰 호재다. 이전에 구매한 EUV 1세대 장비로도 3나노 기술을 도입할 수 있게 되면서 장비 지속성이 늘고, 장비 투자 예산은 아낄 수 있게 된다. 기존 EUV 노광 장비는 1500억원 대를 훌쩍 넘는 고가지만, 차세대 High-NA 장비는 5000억원대에 이를 만큼 가격이 상당히 비싸질 것이란 관측도 나온다.

업계 관계자는 “삼성전자뿐 아니라 값비싼 EUV 시스템 때문에 투자를 망설이던 마이크론 테크놀로지 등도 EUV 도입에 적극적으로 나설 가능성이 있다”며 “EUV 시장이 커질 기회”라고 전했다.

한편 ASML은 차세대 High-NA 노광 장비인 'EXE:5000' 개발에 박차를 가하면서 반도체 EUV 시대에 대응하고 있다.

강해령기자 kang@etnews.com