관련 통계자료 다운로드 3D 적층 기술 비교

관련 통계자료 다운로드 3D 적층 기술 비교

재미 한인 과학자들이 주축이 돼 설립한 미국 벤처기업 비상(BeSang, 대표 이상윤)이 웨이퍼 생산량을 3∼5배 향상시킬 수 있는 기술을 개발했다.

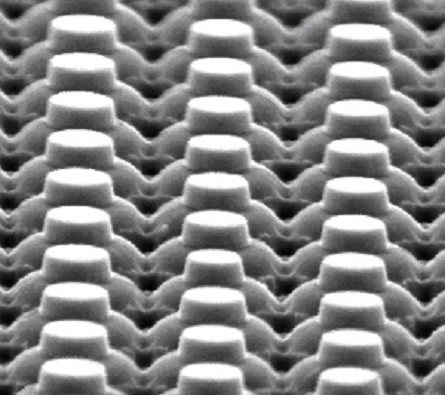

포브스를 비롯한 미국 언론에 소개되기도 한 이 기술은 웨이퍼를 몇 장을 올리는 3D 패키지 적층 기술과는 달리 한 장의 웨이퍼 안에 메모리 회로를 쌓아올려 같은 웨이퍼로도 3∼5배 가량 더 많은 메모리를 생산할 수 있다. 이 기술이 상용화되면 메모리 생산 업체들이 수 조원에 달하는 생산 설비 증설 비용을 절약할 수 있다. 비상은 이 기술을 통해 같은 크기에서 용량을 8배 늘린 노어플래시를 개발해 상용화 가능성을 입증했다.

이 기술은 또 시스템온칩(SoC)에서도 임베디드 메모리를 로직 회로 위에 세울 수 있고 CMOS 이미지센서(CIS)에서도 메모리를 위에 적층함으로써 CIS가 빛을 받아들일 수 있는 공간을 충분히 확보, 크기가 작으면서도 성능이 우수한 CIS를 개발할 수 있다. 관련기사 인물면

최근 내한한 이상윤 사장은 “레이어와 회로에 열처리를 분리해 적용할 수 있는 독특한 기술을 개발해 3차원 적층에 성공했다.“며 "웨이퍼 표면 층이 다른 웨이퍼 위에 그대로 붙기 위해서는 1000℃이상 고온처리가 필요하지만, 회로를 구성하는 아연이나 알루미늄 구리 등은 400℃를 넘어서면 녹는 성질이 있어 열처리 분리 기술이 필요하다.”고 말했다.

문보경기자@전자신문, okmun@