관련 통계자료 다운로드 삼성 30나노 64기가 낸드플래시 제조 공정

관련 통계자료 다운로드 삼성 30나노 64기가 낸드플래시 제조 공정

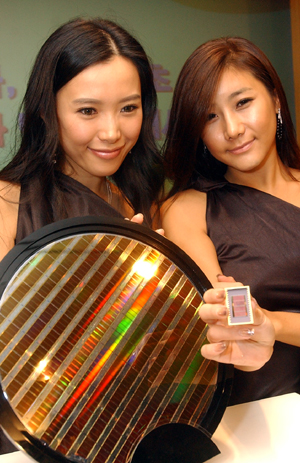

삼성전자가 반도체 분야에서 세계 최초로 30나노대 진입에 성공했다. 30나노는 회로 선폭이 머리카락 굵기의 4000분의 1에 불과한 것으로 기존 기술로는 구현이 불가능하다고 여겨져 마의 벽으로 불렸다.

삼성전자(대표 윤종용)는 23일 기존 미세회로의 공정의 최고치로 여겨진 ‘40나노 벽’을 뚫고 30나노 64Gb 낸드플래시를 개발했다고 밝혔다. ▶관련기사 3면

특히 이번 30나노 64Gb 낸드플래시 개발 성공이 기존 개념과 발상을 새롭게 바꾸는 ‘창의’의 산물이라는 점에서 주목된다.

전준영 삼성전자 반도체총괄 상무는 “반도체의 초미세화·대용량화를 선도하고 있는 삼성전자의 고민은 이를 개발할 수 있는 장비가 존재하지 않는다는 것”이라며 “마의 장벽으로 인식돼 온 ‘40나노 벽’을 허물 수 있었던 것은 ‘창의적 발상’이었다”고 밝혔다.

<뉴스의 눈>

삼성전자는 30나노 64Gb 낸드플래시 개발에 기존 60나노 공정 장비를 활용했다. 아직 전 세계적으로 30나노대 공정 장비는 존재하지 않기 때문이다.

반도체 회로를 현상해내는 광원으로는 50나노공정까지는 아르곤 플루오린(ArF) 또는 엑시머 레이저가 사용됐다. 40나노대에서는 기존 ArF 광원을 응용한 이머전(액침기술) 방식이 쓰일 예정이다. 그러나 머리카락 굵기의 4000분의 1 정도인 회로선을 만들어야 하는 30나노대 공정에서는 원자외선(EUV)이 광원으로 유력하나 상용화되기까지는 몇 년 더 시간이 걸릴 전망이다. 현 추세대로라면 30나노대 공정 장비는 오는 2010년 이후에나 나올 것으로 예상된다.

이에 따라 삼성전자는 자가정렬이중패턴기술(SaDPT:Self-aligned Double Patterning Technology)이라는 독자적인 기술을 개발, 적용했다. SaDPT는 1차로 60나노 간격의 패턴을 두 줄 형성하고 30나노씩 옆으로 움직이며 그 사이에 2차로 패턴을 형성하는 것으로 기존 공정을 활용하면서도 미세회로 공정을 진화시킨 것이다. <그림>. 60나노 장비로 30나노 간격의 회선을 그리게 되는 셈이다. 기존 이중패턴기술(DPT)이 하나의 셀을 구성하는 데 두 번의 포토(사진 노광) 공정을 하는 데 비해 삼성전자의 SaDPT는 투자비 부담이 큰 노광공정은 한 번에 끝내고 한 번의 노광 공정과 한 번의 산화막 공정(식각공정)으로 30나노 미세회로를 구현하는 것이 경쟁력이다.

그러나 SaDPT 기술을 적용하면 패턴은 30나노 간격을 형성할 수 있지만 반도체 회로 미세화에 따른 셀간 간섭 문제가 새로운 과제로 남는다. 회로가 미세해지면서 노이즈가 시그널에 비해 커져 반도체 오동작을 일으킬 수 있기 때문이다. 삼성전자는 이 문제를 셀간 간섭을 줄이는 CTF(Charge Trap Flash) 기술로 극복했다. CTF 기술은 삼성전자가 40나노 미세회로 공정에도 적용한 바 있는데 부도체인 나이트라이드(N)에 전하를 채우는 새로운 방식이다.

전준영 상무는 “30나노 회로 형성에 필요한 새로운 광원을 사용하려면 시간이 더딘데다 장비 개발비가 기하급수적으로 올라가기 때문에 이번에 개발된 기술은 당분간 삼성전자가 시장 지배력을 강화하는 데 결정적인 역할을 할 것”이라고 설명했다.

심규호기자@전자신문, khsim@