메모리반도체의 양산 비용을 지금의 20% 수준으로 낮출 수 있는 3차원(3D) 집적회로(IC) 상용화 기술을 국내외 연구진이 개발했다.

상용화하면 칩 단가는 물론이고 설비 투자 규모도 대폭 낮추고 패턴 축소에 한계에 이른 CMOS 반도체 기술을 대체할 획기적인 기술로 평가됐다.

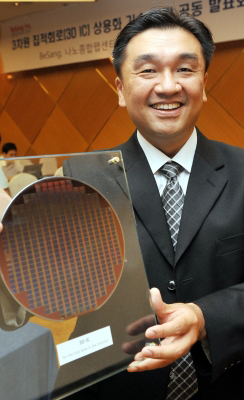

재미 한인 과학기술자들이 만든 팹리스 업체인 비상(대표 이상윤 www.besang.com)은 나노종합팹센터(NNFC·소장 이희철), 스탠퍼드나노팹(SNF)과 공동으로 ‘3차원 집적회로(3D IC) 상용화 기술’을 세계 최초로 개발했다고 11일 발표했다.

국제전기전자기술자협회(IEEE) 종신 펠로인 사이먼 지 교수는 전자신문 기자와 전화 통화에서 “3D IC는 많은 사람이 수십년간 시도하다 실패했던 기술이어서 이번 개발은 매우 중요하다”면서 (반도체 제조사들이 적용할 경우) 2차원(2D) IC에 비해 경제적 이점이 상당할 것”으로 기대했다.

이 기술은 수직 형태의 반도체 소자뿐 아니라 상부 및 하부에도 배선을 할 수 있도록 하는 완전한 3D IC 기술이다. 단순한 3D패키지가 아닌 3D IC를 일반 CMOS 팹에서 사용하는 것과 동일한 기술을 적용해 높은 수율을 확보할 수 있다고 비상 측은 설명했다. 비상은 일반적인 2D IC에 비해 칩 생산 단가를 80% 낮출 수 있으며 기존 팹 설비를 그대로 쓰기 때문에 막대한 팹 건설 비용도 줄일 수 있다고 주장했다. 또 CPU나 시스템온칩(SoC) 안에서 로직 제품과 함께 쓰는 임베디드 메모리로 활용할 수 있다고 덧붙였다.

이상윤 비상 사장은 “3D IC 기술은 대규모 작동 블록을 사용하는 메모리 어레이나 이미지센서의 포토다이오드, SoC, CPU 등 첨단 반도체 칩의 메모리 컨트롤 로직회로 제품 제조를 간소화하고 생산 비용을 절감하는 돌파구가 될 전망”이라고 내다봤다.

비상은 업계 표준인 180나노 CMOS 기술과 8인치 웨이퍼를 이용해 이 기술을 구현했다. 전 공정은 400도 이하의 저온공정으로 이뤄졌다. 각각의 반도체 집적회로 안에 약 1억2800만개의 수직 구조의 반도체 소자를 포함했다. 또 금속배선 층을 포함하는 실리콘반도체 기판에 서브마이크론(1마이크로미터 미만)의 두께를 가진 단결정 실리콘층을 형성한 후 실리콘층에 고성능에 신뢰성이 높은 반도체 소자를 형성함으로써 단일 칩 3D IC를 구현했다.

미 스탠퍼드 나노팹은 지난해 초 3D IC 기술의 개념을 시현했으며, 국내 나노종합팹센터가 지난해 7월부터 상용 기술의 개발을 시작했다.

주문정·설성인기자 mjjoo@