‘더 작게, 더 미세하게’를 외치던 반도체에 대한 요구가 한계에 달했다.

1965년 인텔 창업자 고든 무어가 발견한 무어의 법칙은 ‘2년마다 반도체 집적도가 2배가 늘어난다’는 이론이다. 반도체에 집적도가 높아지기 위해서, 다시 말해 더 많은 트랜지스터가 들어가기 위해서는 트랜지스터가 더 작게 설계돼야 한다. 이 때문에 반도체 공정은 계속 미세화돼 20나노대까지 접어들었다. 20나노대 공정은 신호가 흐르는 선과 선간의 간격(선폭)이 20나노 수준이라는 뜻이다. 그만큼 미세하다. 반도체를 구성하는 선폭이 미세해지면 전력 소모도 줄어든다. 회로를 타고 누출되는 전력이 적기 때문이다. 뿐만 아니다. 하나의 웨이퍼에 많은 반도체를 그려 넣을 수 있다. 생산성이 높아진다는 뜻이다.

하지만, 선폭이 미세해지는 것도 물리적인 한계가 있다. 업계에서는 대략 10나노대가 기존 기술로 구현할 수 있는 가장 미세한 선폭으로 보고 있다. 그렇다면 더 이상 반도체에는 발전이 없는 것일까.

대안으로 떠오르는 것이 바로 3차원 반도체다. 3차원 반도체 종류는 여러가지다. 반도체를 3차원으로 쌓아올려서 같은 실장 면적에 더 많은 능력을 갖게 하는 방식이다. 현재 반도체를 여러개 수직으로 쌓고 가운데 구멍을 뚫은 상태에서 회로를 넣어 연결하는 TSV((Through Silicon Via) 방식이 많이 시도되고 있다. 삼성전자는 이 방식으로 패키징한 D램 메모리를 개발해 마케팅 하고 있다. 아직 양산을 시작한 것은 아니지만 TSV 시대가 열리는 것은 머지 않았다는 게 전문가들 시각이다.

이런 방식뿐만 아니라 한 장의 웨이퍼에 회로를 입체적으로 쌓아올리는 3D-IC도 있다. 한국인이 미국 실리콘밸리에 설립한 ‘비상’이라는 벤처기업이 이 기술을 개발해 화제가 됐다.

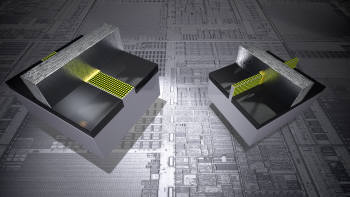

트랜지스터 자체를 3차원으로 개발하는 방식도 나왔다. 이것이 지난 5월 5일 인텔이 발표한 트라이게이트다. 핀이 마치 비늘처럼 튀어나와 그 주변으로 전류가 흐르게 된다. 또, 도선을 수직으로 배열해 트랜지스터 단위 면적을 줄이는 효과도 거뒀다.

무엇보다 놀라운 것은 내년이면 소비자들도 이 방식으로 생산한 프로세서를 만나게 될 것이라는 점이다. 인텔은 내년 출하할 프로세서 ‘아이비브리지’를 이 방식으로 생산한다고 밝힌 바 있다. 이러한 3차원 방식이 당분간은 반도체 기술 혁신에 상당한 영향을 끼칠 것으로 보인다. 하지만, 3차원 방식이 반도체 기술 혁신의 완전한 해답은 아니다.

8나노 이하가 되면 더 이상은 실리콘에서 구현하기 힘들 것이라는 예측이 나오고 있다. 물론 이에 대해서도 여러 가지 시각이 있다. 과거에는 나노대의 반도체는 나올 수 없다는 예측도 있었다. 현재 미세공정이 지속적으로 발전하고 있는 것처럼 기술적인 해결방법을 찾게 될 것이라는 분석이다. 또 한쪽에서는 전혀 새로운 물질로 반도체를 만들어야 혁신이 가능할 것이라는 의견이 나온다. 반도체 기술이 어느 수준까지 발전할 것인지는 IT뿐만 아니라 인류 미래사회를 위해서도 큰 관심사다.

문보경기자 okmun@etnews.com