생산성을 6.5배 높이고 제조 비용을 대폭 절감할 수 있는 차세대 반도체 패키징 기술이 국내 개발됐다. 가로세로 600㎜ 사각형 대형 패널로 고생산성·정밀도를 동시 구현했다.

과학기술정보통신부 산하 한국기계연구원(원장 류석현)은 600㎜ 대면적 패널 위에 고집적 다차원 3D 반도체 패키징을 실현할 수 있는 '팬아웃 패널 레벨 패키징(Fo-PLP)' 본딩 및 검사장비, 공정·소재기술 등 핵심 원천기술과 실용화 기술을 개발했다고 26일 밝혔다.

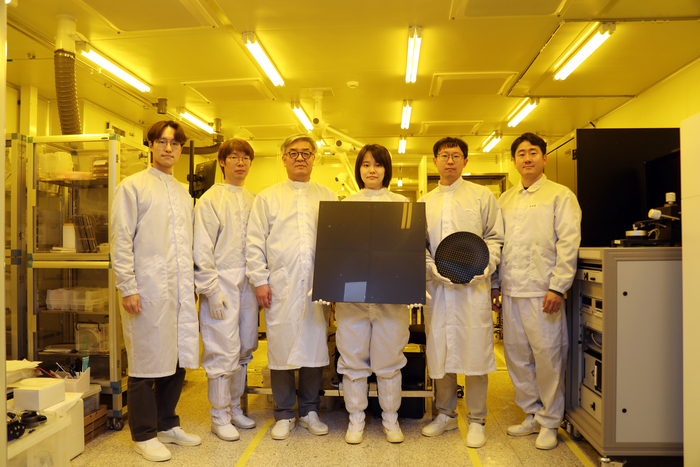

송준엽 자율제조연구소 반도체장비연구센터 연구위원 및 이재학 박사팀이 한화정밀기계, 크레셈, 엠티아이, 네페스와 이룬 성과다.

FO-PLP는 반도체 칩을 대면적 패널 위에 배열해 패키징을 구현하는 기술이다. 대면적 패널 기반이라 생산성이 높지만 기술 난이도가 매우 높다.

연구진은 대면적 패널을 사용해 생산성을 극대화하면서 ±5마이크로미어(㎛) 이내 정밀도, 시간당 1만개 이상 칩 생산이 가능한 본딩 장비(한화정밀기계), 저잔사 고내열성 소재(엠티아이), 1~2㎛급 분해능을 갖는 고속 대면적 검사장비(크레셈)를 통합 개발 및 적용했다.

FO-PLP 기술은 칩을 대면적 패널에 재분배하면서 칩 접착제 단차, 접착 재배열 오차, 몰딩 시 재료 간 열팽창계수 차이 등으로 '칩 틀어짐' 오차가 발생하고 패키지 수율이 떨어진다.

연구팀은 공정 통합형 인공지능(AI) 검사·보정 기술로 칩 틀어짐 오차를 감소시켜 수율·생산성을 높였다. 칩 틀어짐 ±5㎛ 수준 정밀도를 달성했다. 이는 기존 대비 30% 이상 개선된 수준이다. 또 고속 칩 틀어짐 검사·보정 기술로 고도정밀도를 확보, 생산성을 해외 선진사 대비 30% 이상 높였다.

기존 300㎜ FO-WLP보다 생산성을 6.5배 향상시켜 패키지 제조비용도 대폭 줄였다. 선폭을 세계최고 수준인 7㎛ 이하로 미세화해 향후 고성능 하이엔드 패키지에도 적용이 가능할 전망이다.

기계연은 이와 관련, 26일 서울 엘타워 루비홀에서 성과보고회를 개최하고 한국반도체연구조합 및 한화정밀기계, 크레셈, 엠티아이, 네페스와 차세대 반도체 FO-PLP 기술 실용화 업무협약을 체결했다. 각 기관이 상용화에 힘을 모으기로 했다.

송준엽 연구위원은 “FO-PLP 시장은 향후 5년간 연평균 성장률이 30%로 예측되는 고성장 분야”라며 “2030년 500억달러 시장이 예상되는 반도체 패키지 시장은 FO-PLP 기술이 선도할 것으로 기대한다”고 밝혔다.

한편, 이번 연구는 산업통상자원부 소재부품기술개발사업 'Die Shift 오차보정이 가능한 고정밀 FO-PLP본딩시스템 개발' 과제로 수행됐다.

김영준 기자 kyj85@etnews.com