일본 엘피다가 세계 최고 수준인 25나노 공정 D램 제조 기술을 개발했다고 2일 니혼게이자이가 보도했다. 이 신문은 엘피다가 오는 7월부터 히로시마 공장에서 25나노 기술을 사용한 2기가비트 용량의 D램을 양산할 계획이라고 전했다.

25나노 공정은 기존 30나노 공정에 비해 회로 폭이 좁아 1장의 실리콘 웨이퍼에서 생산 가능한 D램 수가 늘어난다. 엘피다 측은 생산 효율이 약 30% 높아진다고 밝혔다. 이 회사는 아울러 D램 크기가 작아져 스마트폰이나 노트북 등의 소형화에도 도움을 준다고 덧붙였다.

엘피다는 오는 7월 25나노 공정 2기가비트 D램 양산에 이어 연내에는 4기가비트 제품도 내놓는다는 방침이다. 엘피다 측은 “미세 공정화 경쟁이 치열한 D램 시장에서 지난 10년간은 삼성전자가 앞서왔다”라며 “1년 전부터 25나노 공정 기술을 다시 검토한 결과가 성과를 내서 20나노 대에서는 세계 최초로 양산을 눈앞에 뒀다”라고 설명했다.

니혼게이자이는 첨단 제품을 앞서서 만들면 가격 폭락의 영향을 덜 받으며, 이익을 낼 수 있다고 D램 시장을 분석했다. 또 D램 시장이 올해 2월 이후 수요와 가격 모두 회복세를 탔으며, 엘피다가 25나노 신제품으로 PC나 스마트폰 수요를 노린다고 내다봤다.

장동준기자 djjang@etnews.co.kr

<뉴스의 눈>

‘엘피다’발(發) 25나노 D램 개발 소식은 지난 20년여간 국내 업체들이 이끌어온 메모리반도체 기술개발 주도권을 다시 일본에 넘겨줄 수 있는 매머드급 뉴스다.

미세공정 개선은 반도체 웨이퍼에서 생산되는 반도체 칩의 수량이 늘어나 원가 절감으로 직결되고 곧바로 수익성 확대로 이어진다. 가격 싸움이 치열한 메모리 반도체 시장에서 공정 개선을 통한 원가 절감은 결과적으로 전체적인 경쟁력이 강화된다.

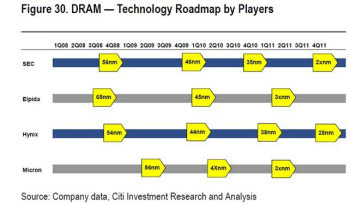

삼성전자와 하이닉스 등 국내 반도체업체들의 D램 공정은 현재 40나노급이 주력이며 하반기부터 30나노급 비중을 확대할 계획이다. 엘피다가 7월부터 20나노급 양산라인을 가동하게 되면 적게는 6개월, 길게는 10개월여 국내 기업이 뒤쳐지게 된다.

그러나 관련 업계와 전문가들은 엘피다의 발표에 강한 의구심을 나타냈다.

엘피다는 지난 2009년말 40나노급 D램을 양산한다고 밝힌 바 있으나 아직까지 시장에서 엘피다산 40나노급 D램 제품을 찾아보기 어려운 상태다. 또 올해 초 30나노 D램을 이달부터 양산한다고 발표하는 등 상식적으로 앞뒤가 맞지 않는 행보를 이어왔다. 발표대로라면 35나노를 양산하는 삼성전자와 38나노를 양산하는 하이닉스 모두 엘피다에 미세공정 기술에서 뒤쳐지는 셈이다.

업계 관계자는 “지난 수년간 엘피다가 발표한 내용에 신빙성이 떨어지는 만큼 이번 개발 소식도 믿기 어렵다”며 “특히, 30나노급 적용도 못한 상태에서 한 단계를 뛰어넘어 20나노급을 양산한다는 것은 현실적으로 불가능에 가깝다”고 말했다.

부족한 투자 여력도 ‘20나노 양산 돌입’을 부정적으로 보는 한 요인이다. 20나노 양산라인을 구축하기 위해서는 엄청난 자금이 소요된다. 그러나 7%대의 영업손실을 기록한 엘피다의 지난 1분기 실적만으로도 외부 수혈 없이는 어렵다는 것이다.

이번 25나노 D램 개발도 엘피다의 주요 자금줄인 대만 업계를 대상으로 추가 투자를 이끌어내기 위한 ‘제스쳐’가 아니냐는 분석이 많다.

박재근 한양대 교수는 “경제성만 배제하면 공정 디자인 패턴을 변형해 20나노급 D램을 개발할 수는 있으나 양산 라인 가동은 완전히 다른 차원”이라며 “이번주 정식 실적발표를 앞두고 있는 엘피다가 장기적인 투자금 확보를 위해 개발 계획을 다소 부풀린 것으로 보인다”고 풀이했다.

서동규기자 dkseo@etnews.co.kr