관련 통계자료 다운로드 메모리 기술 변화 추이

관련 통계자료 다운로드 메모리 기술 변화 추이

‘선폭을 줄여라. 그러면 생존할 것이다.’

반도체 경기가 악화되면서 관련 업계가 원가경쟁력 강화를 위해 미세공정 전환에 총력을 기울이고 있다. 메모리나 마이크로프로세서와 같은 로직 제품의 미세공정 전환 수준은 경쟁력을 나타내는 바로미터다. 메모리 업계 선두권을 유지한 국내 반도체 기업들은 미세공정 전환 수준에서 앞서왔다. 그러나 3, 4위 업체인 마이크론과 엘피다도 바짝 추격하고 있다. 반면에 2008년 반도체 불경기 이후 미세공정 전환에 뒤처진 대만 반도체 기업들은 지난해 말부터 다시 불어온 불황에 맥없이 무너지고 있다. 반도체 회로 선폭을 누가 앞서 줄이느냐에 따라 생존 여부가 사실상 결정되는 셈이다. 가히 총성 없는 전쟁이다. 내년엔 사람 머리카락 굵기 5000분의 1 두께인 20나노급 경쟁이 본격적으로 시작된다. 이 경쟁에서 살아남기 위한 기업들의 치열한 기술개발 상황을 알아본다.

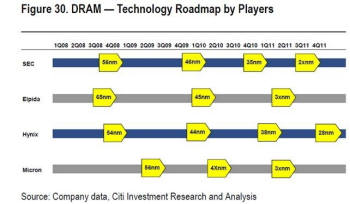

◇촉발된 미세공정 전쟁=메모리 반도체 기업들이 회로 선폭을 줄이는 신기록 경쟁에 돌입했다. 지난 9월 22일 삼성전자가 세계 최초로 20나노급 D램 반도체 양산에 돌입, 경쟁 기업에 비해 6개월 이상 앞서는 기술력 우위를 나타내면서 맨 앞에 나섰다. 기존 30나노 비중은 연말까지 전체 생산량 가운데 절반 이상으로 늘릴 예정이다. 지난해 4월 20나노급 양산에 들어간 낸드플래시도 연말까지 30나노 이하 비율을 70%까지 확대할 계획이다. 내년에는 10나노급 진입으로 자신이 세운 신기록을 다시 갈아치울 방침이다.

경쟁 기업들도 미세공정 전환에 총력을 기울이고 있다. 하이닉스는 올 2분기 30나노급 개발에 힘을 쏟은 결과 9월부터 안정된 전환이 이뤄지고 있다. 연말에는 30나노급 비중을 40%까지 늘리고 20나노급 진입도 준비하고 있다. 20나노급이 주력인 낸드는 연말께 70%까지 비중을 늘리고 연내 20나노 제품 양산이 목표다. 내년 10나노급 양산을 추진하고 있다.

3위 업체인 마이크론도 D램 분야에서 올 1분기부터 30나노급 전환을 시작했다. 삼성전자에 앞서 일본 엘피다는 지난 5월 20나노급 D램 개발에 성공하고 최근에는 20나노급 D램 4Gb 제품을 개발했다고 발표했으나 업계로부터 신뢰를 받지 못하고 있다. 반도체 업체들이 이처럼 미세공정 전환에 힘을 쏟는 것은 단위면적당 생산 물량을 늘릴 수 있는데다가 전력소비 감소, 작동속도 향상 등 여러 이점이 있기 때문이다. 동일한 공정라인에서 회로선폭을 10나노 줄일 때마다 생산량은 30~70%까지 늘어나게 된다. 회로선폭을 줄여 한 웨이퍼에서 더 많은 반도체칩을 만들어내는 것이다.

미세공정 전환 없이 반도체 생산량을 늘리려면 공장(팹)을 새로 건설해야 한다. 단순 계산으로 10나노 선폭을 줄이면 반도체 공장 반 개 정도를 더 세우는 꼴이다. 비용 측면에서는 공장을 새로 짓는 것보다 선폭을 줄이는 것이 두세 배 절감 효과가 있다.

반도체 시장에서 생산량 확대는 가격 경쟁력 강화와 동의어다. 미세공정에 앞서면 생산 원가가 낮아져 경쟁기업에 비해 수익성이 더 높아진다. 동일한 수익이라면 더 저렴하게 판매할 수 있게 된다.

미세공정에 뒤진 대만 반도체 기업들이 최근 감산에 돌입한 것도 가격 경쟁력이 뒤졌기 때문이다. 메모리 가격이 하락하면서 생산원가보다 더 낮아져 만들어낼수록 손해를 보게 돼 결국 생산 자체를 줄이는 극약 처방에 나선 것이다. 반면에 미세공정에 앞선 삼성전자나 하이닉스 등 선두권 기업들은 시장 가격이 하락해도 상당기간은 흑자를 유지할 수 있게 된다. 삼성전자는 30나노에서 20나노급으로 전환되면서 원가 경쟁력이 40% 이상 높아질 것으로 보고 있다. 결국 이로 인해 시장 지배력은 계속 강화된다. 반도체 미세공정은 ‘빈익빈 부익부’ 법칙이 적용되는 셈이다.

◇10나노급에 도전한다=메모리 반도체 기업들에 미세공정 전환은 절체절명의 과제다. 이전에는 30나노급 이하는 물리적 한계로 불가능하다는 평가를 받았다. 그러나 끊임없는 기술개발로 내년에는 20나노급 시장에서 본격 경쟁이 일어나고 10나노급까지 전환이 시도될 전망이다. 10나노 이하부터는 다시 물리적 한계론이 등장하고 있다. 실현 가능성 여부는 미지수지만 계속된 기술개발로 인해 성공 가능성도 배제할 수는 없다.

미세공정 기술은 크게 세 가지 기술을 통해 장벽을 허물고 있다. 우선 노광장비의 성능 향상이다. 웨이퍼에 메모리칩 회로 디자인을 얇게 그리기 위해 파장이 짧은 광원으로 계속 진화하고 있다. 현재 10나노급 D램 공정 전환을 염두에 두고 연구개발 목적으로 극자외선(EUV) 장비를 도입해 개발이 진행되고 있다. 삼성전자는 2002년부터 EUV 연구개발에 들어가 지난해 세계 최초로 EUV 노광장비를 도입해 차세대 D램 양산 적용을 목표로 연구개발 중이다. 지난 6월에는 삼성전자, 하이닉스, 인텔, 도시바, TSMC 등 주요 반도체업체가 일본 도시바, 호야 등 11개 업체가 출자해 만든 조인트벤처 EIDEC(EULV Infrastructure Development Center:극자외선 노광기술기반 개발센터)에 참여, 10나노급 반도체 기술을 공동 개발하기로 했다.

EUV는 파장이 13.5㎚로 현재까지 사용된 광원 중에서 가장 파장이 짧다. 350나노 시절에는 365㎚ 파장인 ‘i Line’이 적용됐다. 이후 KrF(불화크립톤·248㎚), ArF(불화아르곤·193㎚) 등으로 광원이 계속 바뀌었다. 이는 반도체 설계 회로가 미세해지면서 이를 웨이퍼에 그리기 위해 더욱 얇은 붓을 사용하는 것과 같은 뜻이다.

10나노급이라면 머리카락 두께보다 5000분의 1, 많게는 1만분의 1 두께로 디자인을 그릴 수 있는 EUV 광원을 적용, 장비 개발에 사용하게 된다. EUV 장비는 2013년 이후에 양산에 적용이 가능할 것으로 예상된다.

40나노급 이전까지는 ArF 광원을 사용하는 노광기가 적용됐으나 이후에는 한계를 나타냈다.

이를 보완하기 위해 개발된 기술이 ‘이머전(Immersion) 리소그라피’다. 현재는 이머전 장비가 주로 사용된다. 이 기술은 웨이퍼와 마스크 사이에 있는 렌즈에 물을 넣어 빛 굴절률을 높이는 방식이다. 굴절률이 높아지면 초점의 심도가 높아져 더 미세한 디자인 패턴을 세길 수 있게 된다.

더블 패터닝(Double Patterning)도 미세공정 한계를 극복하는 데 톡톡한 역할을 해왔다. 노광공정을 두 차례 시행해 미세회로를 구현하는 기술로 더욱 미세한 공정이 가능해지고 집적도도 끌어올린다. 10나노급으로 나아가면 더블 패터닝을 한 번 더 시행하는 ‘더블 더블 패터닝’이 적용될 것이라는 게 전문가들의 전망이다.

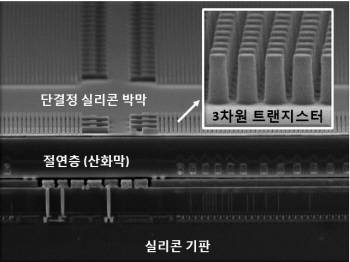

세 번째 기술은 집적도를 높이기 위해 셀을 위로 쌓아 저장공간을 확보하는 3차원(3D) 기술도 개발되고 있다. 3D 기술은 다시 세 가지로 나뉜다. 2차원 칩을 입체적 형태로 변형하는 ‘3차원 트랜지스터’와 반도체 표면 외에 얇은 반도체 박막을 연속으로 형성해 칩을 여러 층 형성하는 ‘3차원 집적회로’, 완성된 칩을 적층해 단일 패키지 안에 여러 개 칩을 넣은 ‘3차원 패키지’ 등이다. 3D 반도체는 노광 공정 장비 가격이 상승하면서 관련 공정 비용도 크게 올라가는 문제를 해결할 수 있는 대안책으로 떠오르고 있다.

◇450㎜ 웨이퍼 ‘시기 미지수’=현재 반도체 생산에 적용되는 가장 큰 웨이퍼는 300㎜다. 미세공정 전환은 동일한 웨이퍼 크기에서 선폭을 줄여 생산량을 늘리는 것이다. 생산량을 확대하는 또 다른 방법은 웨이퍼 크기 자체를 키우는 것이다. 반도체 업계는 6인치(150㎜)→8인치(200㎜)→12인치(300㎜)로 웨이퍼 크기를 키워왔다.

300㎜(12인치) 이후 웨이퍼 크기는 450㎜(18인치)다. 450㎜ 웨이퍼로 공정을 전환하면 웨이퍼당 생산성은 2.25배 늘어난다.

삼성전자를 비롯해 IBM, 인텔, TSMC, 글로벌파운드리스 등이 450㎜ 웨이퍼 전환 기술 개발에 들어갔다. 내년 파일럿 라인 도입을 목표로 삼고 있으나 반도체 시황이 악화되면서 막대한 자금 투자가 필요한 웨이퍼 전환 시기는 아직까지 불투명한 상태다.

<소박스> 대안 기술도 다양화…TSV·신물질 등

메모리 집적화 기술 한계를 극복하기 위해서 선폭을 줄이는 방법 외에 다양한 대안 기술들도 계속 등장하고 있다.

가장 대표적인 것이 신물질 개발이다. 반도체 공정에서 회로와 외부 금속 배선을 연결하는 ‘메탈 공정’에서 기존에 사용하던 알루미늄을 전도성이 높은 구리로 대체하는 방법이다. 회로선폭이 줄어들면서 배선의 저항에도 성능저하가 발생할 수 있기 때문에 저항이 작은 금속 물질로 전환한 것이다. 또, 유전율이 높은 High-k 물질을 메탈게이트에 사용, 누설전류를 줄이고 데이터 처리속도도 높이게 된다.

설계 구조를 바꿔 집적도를 높이고 원가 경쟁력도 강화하기도 한다. 낸드플래시는 초기에 셀이 한 개인 ‘싱글레벨셀(SLC)’ 구조였으나 1개 셀을 두 개로 나눠, 기존보다 데이터 집적도를 두 배 높인 멀티 레벨 셀(MLC) 제품이 주류를 이루고 있다. 동일한 셀 개수에서 집적도를 두 배 향상시킨 것이다. 현재는 1개 셀에 3개의 데이터를 저장하는 트리플 레벨 셀(TLC) 제품까지 나오고 있다. 다만 이 같은 기술은 데이터 용량을 높이는 데는 효과가 있지만 에러율도 동시에 증가한다는 단점이 있다. 새로운 패키지 기술도 집적도 향상에 영향을 준다. 3차원 패키지로 불리는 ‘3차원 실리콘관통전극(TSV)’ 기술은 2개 이상 칩을 수직 관통하는 전극을 통해 칩 간 전기적 신호를 전달하게 된다. 이 기술은 성능은 높아지고 크기는 줄이는 특성이 있어 차세대 대용량 메모리 패키지 기술로 주목받고 있다. 업계 전문가들은 TSV 기술을 이용한 대용량 메모리 제조 기술이 앞으로 2~3년 내에 주력 기술로 부상할 것으로 내다봤다. 메모리반도체·시스템반도체·이미지 센서 등을 하나의 패키지에 통합하는 데 핵심기술이 될 것으로 전망했다. 하이닉스는 올해 초, 40나노급 2기가비트 DDR3 D램을 8단 적층하는 데 성공해 단일 패키지에서 대용량 16기가비트를 세계 최초로 구현했다.

<특별취재팀> 서동규차장(팀장) dkseo@etnews.co.kr, 서한·양종석·윤건일·문보경·이형수기자

![[연중기획-온리원 부품소재를 향해] <4부-4> 공정한계, 이렇게 극복한다](https://img.etnews.com/photonews/1110/193606_20111012143218_189_0003.jpg)

![[연중기획-온리원 부품소재를 향해] <4부-4> 공정한계, 이렇게 극복한다](https://img.etnews.com/photonews/1110/193606_20111012143218_189_0005.jpg)