450㎜(18인치) 웨이퍼 반도체 공정 개발이 급물살을 타고 있다. 삼성전자·인텔·TSMC·글로벌파운드리즈·IBM이 주축이 된 `글로벌450㎜컨소시엄(G450C)`이 올해 본격 가동된다. 오는 3월경 미국 뉴욕주립대 나노스케일 사이언스 엔지니어링 대학(CNSE)에 450㎜ 웨이퍼용 전용 테스트 공장(팹)이 완공되면 장비·공정 개발이 시작된다. 지난해 인텔·삼성전자·TSMC는 핵심 공정 장비인 노광(리소그래피) 장비 개발을 위해 ASML에 총 64억3900만달러를 투자했다.

웨이퍼 대구경화는 필연적인 기술 발전 추세로 인식돼 왔지만, 공정 전환에는 아직도 기술적 난제가 적지 않다. 3회에 걸쳐 450㎜ 웨이퍼 공정으로 이행하는데 풀어야 할 과제를 짚어 보고 국내 업계의 대응 방안을 집중 진단한다.

◇450㎜ 웨이퍼 왜?

반도체 미세 공정 기술은 회로 선폭이 10나노미터(nm) 대에 진입하면서 한계에 봉착했다. 한 개 반도체에 여러 기능이 통합되면서 수율에도 비상이 걸렸다. 모바일 애플리케이션프로세서(AP)나 PC 중앙처리장치(CPU)는 300㎜ 웨이퍼 하나 당 칩 한 개도 건지지 못하는 경우가 비일비재하다. 다이(Die 웨이퍼에서 칩 하나에 해당하는 부분)가 커서 웨이퍼에 남는 공간도 많다. 지금보다 웨이퍼가 커지면 수율·생산성·가격 경쟁력을 한꺼번에 개선할 수 있다.

업계 전문가는 “시스템온칩(SoC)으로 각종 기능이 집적화 되면서 웨이퍼 크기를 늘려 수율을 개선해야 한다는 요구가 시스템 반도체 업계를 중심으로 일고 있다”고 말했다. 실제 애플·인텔 등 AP·CPU 업체들은 최대한 빨리 450㎜ 웨이퍼 공정 도입을 원한다.

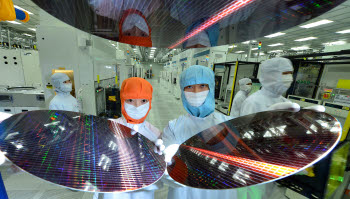

글로벌450㎜컨소시엄(G450C)은 450㎜ 웨이퍼 공정 표준 규격을 발표했다. 450㎜ 웨이퍼는 면적이 현재 300㎜보다 2.25배 넓다. 웨이퍼 한 장에서 많은 칩이 나오기 때문에 전체적으로 어림잡아 양산 비용을 30% 낮출 수 있다는 계산이 나온다.

◇걸음마 단계인 개발 속도

아직 바꿔야 할 게 너무 많다. 업계는 지난해부터 공정용 툴(tool) 테스트를 시작했다. 올해부터는 장비를 본격 제작한다. 오는 2015년에는 공정 설계 연구개발(R&D)이 시작된다. 초도 생산은 오는 2017년께나 가능할 전망이다. 업계는 2018년 양산을 목표로 한다. 개발 진척도는 이제 걸음마 단계다. 필수 재료인 잉곳과 웨이퍼는 이미 개발돼 있다. 일본 섬코·시네츠, 한국 LG실트론 등 실리콘 웨이퍼 공급업체 대부분 표준에 맞는 웨이퍼를 생산하고 있다. 웨이퍼를 담는 용기도 개발 완료됐다. 포스비(FOSB Front Opening Shipping Box)와 팹 내에서 웨이퍼를 운반하는 풉(FOUP), 두 기능을 합친 맥(MAC Multiple Application Carrier)은 미국 인테그라스가 제작해 CNSE에 공급한다.

그러나 장비는 준비된 게 전혀 없다. ASML에 따르면 가장 중요한 극자외선(EUV) 리소그래피 장비는 오는 2015년께나 개발될 전망이다. 한국의 유진테크처럼 이미 450㎜용 장비 개발을 시작한 곳도 있지만 대부분 초기 R&D 수준이다.

오은지기자 onz@etnews.com