IBM이 세계 최초로 반도체공정의 한계로 여겨지던 10나노미터의 벽을 깼다.

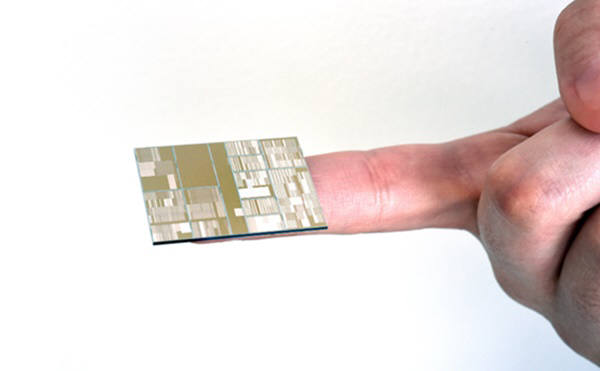

뉴욕타임즈는 9일(현지시간) IBM이 반도체 회로선폭이 7나노(1나노=10억분의1)미터인 반도체칩 워킹샘플(시제품) 개발에 성공, 이를 공개했다고 보도했다. 이 공정 완료시점까지 총 30억달러(3조4천억원)가 투입된다.

그동안 반도체업계에서는 반도체 미소화 공정이 진전되더라도 회로선폭 10나노미터 이하 공정실현은 쉽지 않을 것으로 보았다. 하지만 IBM은 7나노미터 회로선폭의 반도체 칩 시제품으로 `서브10’(10나노미터 이하 공정) 회로 선폭을 처음 실현했다. 이로써 한계에 부딪친 것으로 여겨진 무어의 법칙(`반도체집적도는 2년마다 배로 증가한다`는 법칙)도 돌파구를 찾게 됐다.

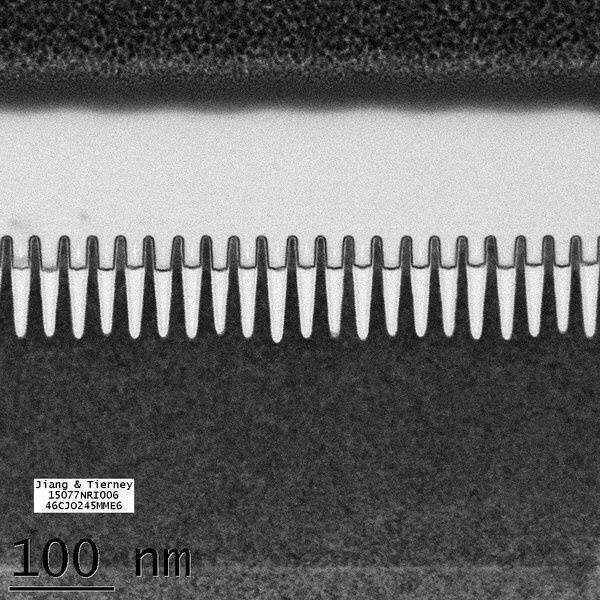

7나노반도체는 순수한 실리콘 대신 실리콘-게르마늄 소재 웨이퍼로 만들어졌다. 이론적으로는 200억개 이상의 트랜지스터까지 집적된다. 이 칩에는 기존 최고의 미세 반도체 공정으로 꼽히는 삼성의 14나노 공정에서 생산된 칩의 4배나 되는 트랜지스터를 집적할 수 있다. 또 회로구성 면적은 10나노공정의 절반으로 줄어들게 된다.

7나노미터 공정 회로선폭의 크기는 우리 몸에 있는 지름 2.5나노미터인 DNA 한 가닥의 길이 정도가 된다. 혈액속의 적혈구는 지름은 7천500나노미터 크기다.

7나노미터 반도체생산은 인텔이 코드명 캐논레이크(Cannonlake)개발작업을 진행하면서 내년 말 내놓을 내놓을 10나노미터 노드에 이은 차차기 반도체 공정이 될 전망이다.

기존 반도체 공정 가운데 가장 미세한 공정에서 생산된 반도체는 삼성의 갤럭시S6용 엑시노스7420칩이다.

서브해시시 미트라 스탠포드대 전기공학과 로버스트시스템그룹 이사는 “나는 별로 놀라지 않는다. 이는 정확히 예상 로드맵대로 간 것이기 때문이다. 하지만 이는 환상적이다”라고 말했다.

IBM의 혁신적 미세반도체 개발은 IBM 주도하에 뉴욕주,글로벌파운드리,삼성 컨소시엄이 공동으로 이뤄낸 성과다. 하지만 IBM측은 언제 상용화 칩을 내놓을지에 대해서는 확답하지 않았다. 올초 타이완 TSMC는 오는 2017년도에 7나노급 반도체 시험생산을 할 예정이라고 발표했지만 아직 아직 시제품조차 내놓지 못하고 있다.

한편 IBM은 반도체 생산공정을 글로벌파운드리에 매각했으며 지난 주에 법적 이관 절차가 완료됐다.

컨설팅그룹 인비저니어링 시포드N.Y.의 리처드 도허티는 “BM은 이 7나노칩 개발로 `말주인`이 아닌 `신사 도박사`의 위치에 서게 됐다. IBM은 여전히 반도체 레이스를 펼치고 싶어한다”고 말했다.

IBM은 이제 이 기술을 바탕으로 글로벌 파운드리를 비롯, 브로드컴, 퀄컴,AMD 등을 대상으로 기술 라이선스 사업을 할 수 있게 됐다. 전세계 반도체업계는 IBM의 7나노미터 반도체 공정에 사용된 실리콘-게르마늄이 최적의 재료인지에 대해 판단해야 한다.또한 원자 크기(0.25나노미터)에 점점 근접해 가는 해상도를 갖는 칩의 패턴 형성(에칭)을 위해 EUV(Extreme Ultraviolet)광 공정으로 전환할지에 대해서도 고민해야 한다.

무케시 카레 IBM반도체 연구담당부사장은 “이제 IBM컨소시엄은 7나노칩 상용 생산을 위해 EUV광 사용을 계획하고 있다”고 말했다. 그는 “EUV는 또다른 혁신적인 변화를 가져올 기술이다. 지금까지 시연은 연구소에서만 이뤄졌다. 최종목표는 내년 말 나올 10나노공정 칩에 비해 절반의 회로면적을 실현하는 것이다”라고 말했다.

전자신문인터넷 이재구국제과학전문기자 jklee@etnews.com