국내 연구진이 이진법 컴퓨터 한계를 극복할 수 있는 멀티레벨 트랜지스터 소자를 개발했다.

성명모 한양대 교수, 조경재 텍사스주립대 교수 연구팀은 하이브리드 반도체 초격자 구조 신소재를 이용, 새로운 작동 원리의 멀티레벨 트랜지스터 소자를 개발했다고 15일 밝혔다.

반도체 집적회로 성능 향상을 위해 단위 소자를 더 작게 만들고 면적 당 소자의 수를 증가시키는 노력이 이어졌다. 이런 방식 집적화는 전력 소모와 발열이 생겨 성능 저하를 야기했다.

이 문제를 피하고자 상전이 소자, 신경망 컴퓨터, 양자컴퓨터 등을 비롯해 0과 1의 두 가지 입력에서 벗어나 다중 입력을 이용하는 멀티레벨 컴퓨터가 주목받았다. 멀티레벨 컴퓨터는 이진법 컴퓨터보다 소자 수가 크게 줄어 전력 소모를 절감하고 연산 효율을 증대시킬 수 있다. 다만 제조 공정 난이도가 높고 한정된 동작 온도 등이 실용화 걸림돌로 작용했다.

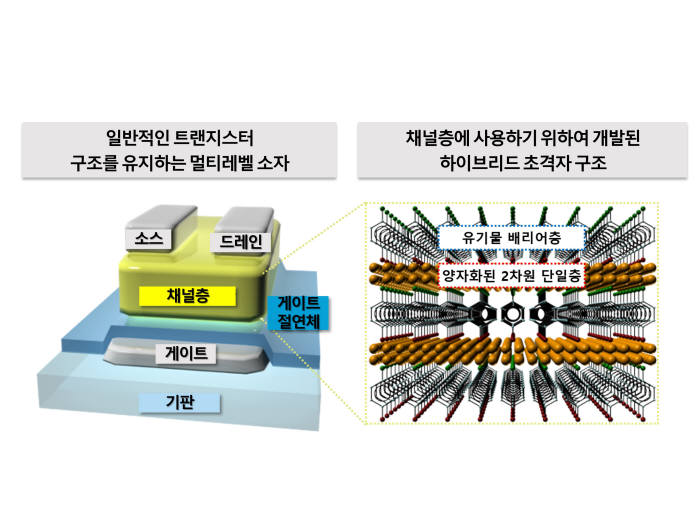

연구팀은 초격자 구조 반도체 소재로 일반적 트랜지스터 구조를 유지하는 동시에 멀티레벨 전도도를 구현할 수 있는 멀티레벨 트랜지스터 소자를 개발, 한계를 극복했다.

2차원 산화아연(ZnO)층에 유기물층을 위아래로 적층한 초격자 박막을 사용해 트랜지스터를 제작한 뒤, 산화아연층이 적층된 순서대로 활성화될 때마다 전도도가 차례로 증가하는 멀티레벨 트랜지스터를 구현했다.

멀티레벨 소자는 기존 이진법 소자 트랜지스터와 동일 구조를 가진다. 그러면서도 멀티레벨 소자 제조 공정이나 대면적, 연속 공정이 불가능한 한계를 극복했다.

성명모 교수는 “이 연구를 통해 완전히 새로운 원리로 작동하는 멀티레벨 컴퓨터를 구현할 수 있는 트랜지스터 소자를 제안했다”면서 “멀티레벨 소자가 실용화된다면 초저전력 반도체와 소재, 장비, 센서, 고성능 로직 반도체 등 반도체를 이용하는 모든 산업에서 획기적인 발전을 가져올 것으로 기대한다”고 설명했다.

이번 연구 성과는 과학기술정보통신부·한국연구재단 미래소재디스커버리사업의 지원으로 수행했다. 국제학술지 '네이처 커뮤니케이션즈(Nature Communications)' 4월 30일자에 논문으로 실렸다.

최호 정책기자 snoop@etnews.com