차세대 칩으로 주목받는 실리콘카바이드(SiC) 반도체의 정전기 방전을 최소화할 수 있는 기술을 국내 연구진이 세계 최초로 개발했다. SiC는 고온과 고압에서 기존 실리콘보다 잘 견디는 장점이 있지만 정전기 손상에 취약하다는 게 단점으로 꼽혀왔다. 이번 개발로 SiC 칩의 단점을 대폭 개선해 응용 분야를 넓힐 수 있게 됐다.

5일 업계에 따르면 구용서 단국대 교수 연구팀은 SiC 기반 전계효과트랜지스터(모스펫), 사이리스터(SCR) 구조의 새로운 정전기 방전(ESD) 보호 소자를 세계서 처음으로 개발했다. 이 연구는 산업통상자원부 신산업창출형 파워반도체 상용화 기술개발 사업 일환으로 진행됐다.

SiC는 차세대 전력 반도체 소재다. SiC 반도체는 기존 실리콘 칩보다 밴드갭이 3배가량 넓은 3.4eV의 광대역밴드갭(WBG)을 가지고 있다. 고온, 고전력, 고전압, 강한 방사 조건 등 극한 환경에서 칩 구동이 안정적이다. 기존 칩보다 크기를 최대 10분의 1로 줄일 수 있다는 특징도 있다.

하지만 SiC 칩은 물리적 특성상 정전기로 인한 칩 손상에 취약하다는 지적이 있었다. ESD는 반도체 설계에서 반드시 고려해야 할 항목이다. ESD 현상이 지속되면 높은 전류 밀도를 갖는 칩이 충격을 받아 열 폭주와 칩 기능 손상을 초래할 수 있기 때문이다.

범용으로 쓰이는 실리콘 기반 칩은 ESD 보호를 위한 연구가 상당히 진전됐다. 그러나 SiC 기반의 ESD 보호 기술은 기술적 난도로 발전이 미진해 대안이 필요한 상황이었다.

구 교수 연구팀은 모스펫과 SCR의 구조적 개선과 새로운 반도체 설계 기법으로 SiC 특성은 유지하면서 ESD 손상을 최소화하는 기술을 발표했다. 이 연구 결과의 일부는 전기전자기술자협회(IEEE) 저널에 게재됐다. 향후 SiC 기반 집적회로(IC) 기술을 개선할 수 있는 연구 결과라는 평가다.

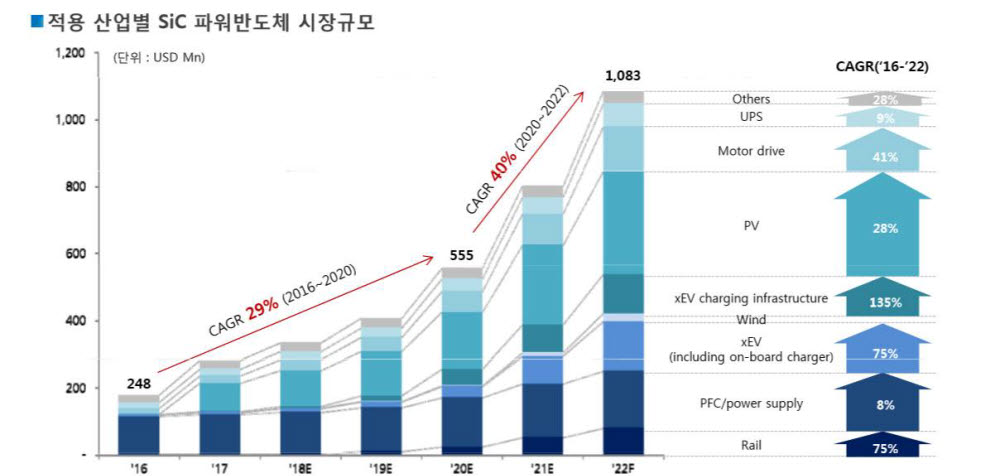

구 교수는 “SiC 기반 ESD 보호소자의 안전동작영역(SOA)이 확보되면서 적용 분야는 매우 광범위할 것으로 예상된다”면서 “특히 전기차, 신재생 에너지 시스템, 우주항공, 심층 시추 등에서 응용 가능성이 매우 높다”고 말했다.

강해령기자 kang@etnews.com