국내 연구팀이 고순도 소재 박막 양면을 모두 반도체 소자로 만드는 기술을 개발했다. 반도체 성능을 획기적으로 향상시킬 수 있는 기술로 평가받고 있다.

포스텍(POSTECH·총장 김무환)은 김석 기계공학과 교수 연구팀이 미국 일리노이대 어바나-샴페인캠퍼스와 버지니아대와 공동연구를 통해 자체적으로 박리되는 고순도 실리콘 박막을 기판 위에 옮기는 전사 기술을 개발했다고 20일 밝혔다.

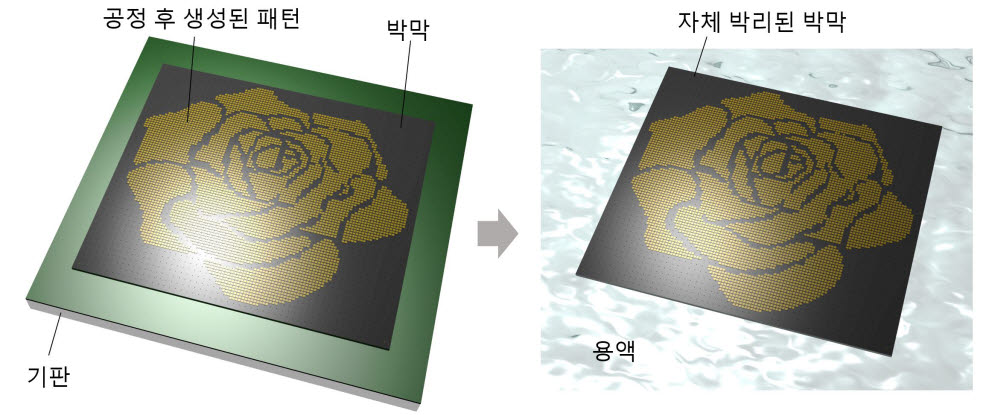

연구팀은 박막, 기판, 그리고 이들이 담긴 용액의 표면 물성을 고려해 조합한 결과, 건조한 상태에서 기판에 강하게 붙어있던 박막이 용액 안에서 자체적으로 떨어져 나갔다.

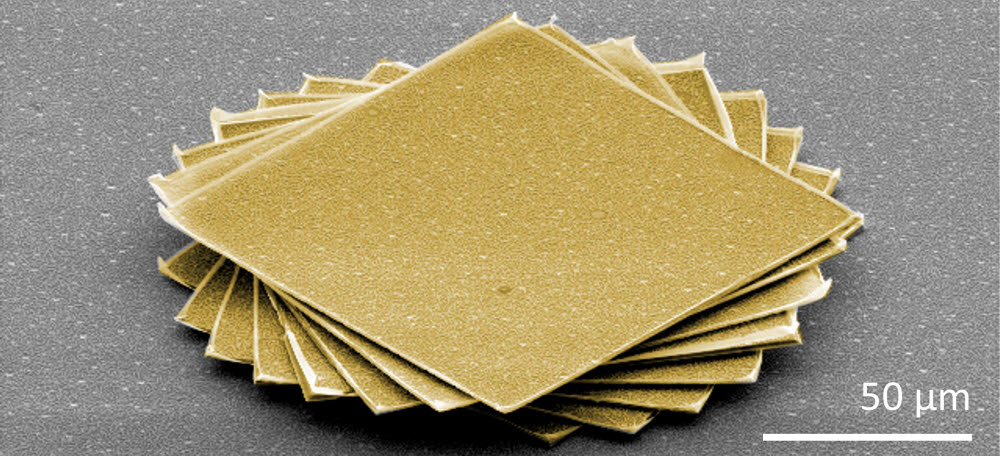

박막을 앞면이 위로 향하게 기판 위에 전사한 뒤 반도체 공정 후, 용액 안에 넣고 자체 박리된 박막을 뒤집었다. 뒤집힌 박막을 용액에서 꺼내 다시 공정 기판에 뒷면이 위로 향하게 전사함으로써 양면에 반도체 공정을 할 수 있었다.

연구성과를 활용하면 실리콘뿐만 아니라 GaN(질화갈륨), 갈륨비소(GaAs) 등 고순도 반도체 소재 박막 양면에도 반도체 공정을 할 수 있다.

이 기술은 3차원 집적회로 개발에도 활용할 수 있다. 2차원 구조 반도체를 3차원 구조로 전환해 제작한 3차원 집적회로는 동일한 실리콘 웨이퍼 면적에 2차원 집적회로 대비 더 많은 반도체 소자를 구현할 수 있는 게 특징이다.

3차원 집적회로는 성능을 높이고 제조 비용을 낮출 수 있는 기술로 주목받고 있지만, 그동안 공정의 복잡성 등의 이유로 개발하기 어려웠다. 성능이 높은 반도체 소자와 소자의 정확하고 신속한 전사, 표준화된 공정이 필요하기 때문이다. 개발된 기술로 반도체 소자의 성능을 높이면 3차원 집적회로 개발에 한 걸음 더 다가갈 수 있다.

김석 교수는 “이 기술은 향후 성능이 높은 3차원 반도체나 마이크로 LED 디스플레이 제조 공정에 사용할 수 있을 것”이라고 말했다.

BK21 사업 지원을 받아 진행된 이번 연구 결과는 최근 국제학술지 네이처의 자매지 '네이처 커뮤니케이션스'에 게재됐다.

포항=정재훈기자 jhoon@etnews.com