한국과학기술원(KAIST·총장 이광형)은 신소재공학과 강지형 교수, 미국 버클리 대학교 문재완 박사와 미국 스탠퍼드 대학교 제난 바오 교수 공동연구팀이 고분자 반도체와 회로기판 경계면을 개선하는 새로운 계면 개질법을 개발하고, 이를 이용해 고성능 스트레처블(늘어나고 유연한) 고분자 반도체를 구현했다고 24일 밝혔다.

고분자 반도체는 기존 실리콘 기반 반도체와 다르게 탄소를 기반으로 구성돼 있으며, 상대적으로 낮은 가격과 대면적 공정이 가능하다는 장점으로 인해 추후 유연 소자, 태양전지, OLED 등의 산업에 응용될 수 있는 차세대 반도체 재료다.

하지만 전기적 성능이 좋은 고분자 반도체는 작은 응력에도 쉽게 깨지는 문제점이 있었다. 일반적으로 고분자 반도체는 결정구조를 많이 가질수록 전기적 성능이 좋아지지만, 이러한 결정구조는 고분자 반도체가 응력에 취약해지게 만들기 때문이다.

이러한 문제점을 해결하기 위해, 기존에는 분자구조의 변화, 첨가제 등을 이용해 고분자 반도체 자체의 기계적 물성을 변화시키는 데 주로 초점을 맞춰왔다.

기존 방법들은 기계적 물성이 향상되는 대신 전기적 성질이 악화되고, 각각의 고분자 반도체에 맞는 분자구조를 찾는데 많은 시간이 소요돼 고성능 스트레처블 고분자 반도체 구현에 적합하지 않았다.

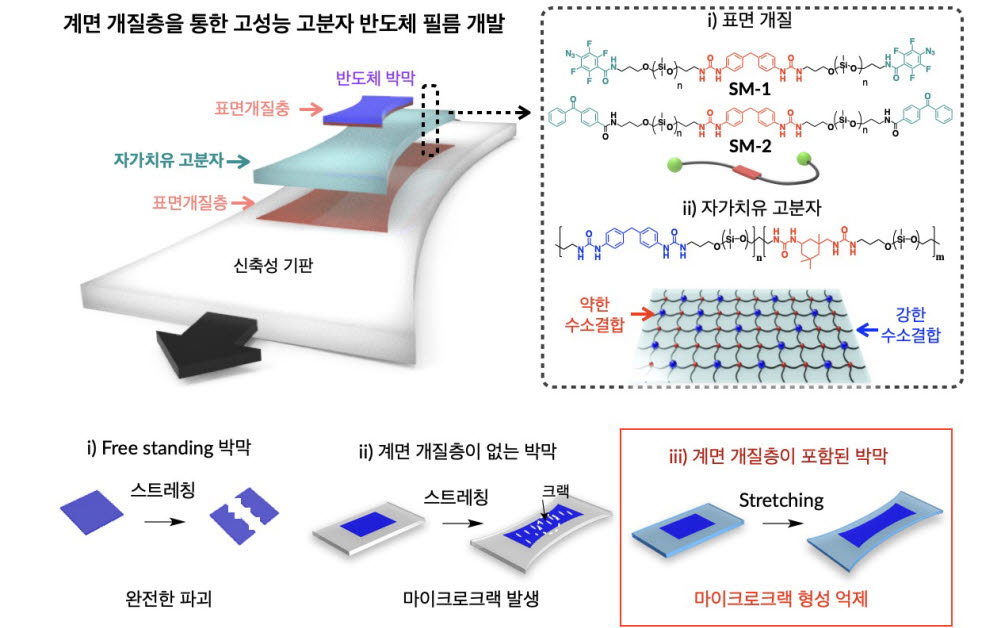

KAIST 강지형 교수와 스탠퍼드 대학교 제난 바오 교수 공동연구팀은 이번 연구에서 고분자 자체의 성질을 변화시키는 것이 아닌 기판과 고분자 반도체 사이의 계면을 개질하는 새로운 방법을 제시했다. 이러한 계면 공학법을 통해 고분자 반도체는 전기적 성질을 잃지 않으면서 기계적 물성이 크게 개선됐다.

공동연구팀은 이번 연구에서 응력에 의해 고분자 반도체가 손상을 받는 것은 고분자 박막과 기판 사이 계면에서의 박리 현상과 그로 인한 응력의 편재화(localization)에 의해 상당 부분 기인함을 발견했다.

공동연구팀은 이러한 문제점을 극복하기 위해 고분자 반도체 박막과 기판 사이의 계면에 새로운 고분자 층을 도입했다. 이 고분자 층은 반도체 박막과 기판 모두와 강하게 결합해 두 층의 박리현상과 응력의 편재화를 효과적으로 막아줬으며, 동역학적 결합(dynamic bond)을 할 수 있는 구조를 가져 추가적인 응력 분산 효과를 보였다.

이러한 계면 개질이 이뤄진 고성능 고분자 반도체는 최대 110%의 변형률까지 눈에 띄는 균열이 발견되지 않았으며, 이는 기존의 같은 반도체가 30% 변형률에서 상당한 균열을 보인 것에 비하면 획기적인 발전이다. 또한 이러한 접근법은 특정 고분자 반도체에 국한되지 않고, 다양한 고분자 반도체, 고분자 전도체, 금속 전도체에 모두 적용 가능하다는 장점이 있다.

KAIST 신소재공학과 강지형 교수와 스탠퍼드 대학교 문재완 박사가 공동 제1 저자로 참여한 이번 연구 결과는 나노 재료 분야 저명 국제 학술지 '네이처 나노테크놀로지' 11월 10일자 온라인판에 게재됐다.

강지형 교수는 “이번 연구는 스트레처블 고분자 반도체 구현을 위한 설계 방향을 새롭게 제시했다는 점에서 의미가 있다”면서 “이번에 개발된 계면 공학법은 급속도로 성장하고 있는 유연소자 시장에 게임 체인저가 될 것으로 기대된다”고 말했다.

한편 이번 연구는 한국연구재단의 우수신진연구사업, 나노소재기술개발사업 미래기술연구실, 삼성종기원 과제의 지원을 받아 수행됐다.

김영준기자 kyj85@etnews.com