삼성전자가 3나노 2세대 공정 상용화에 진전을 이뤄냈다. 내년 가동 예정인 3나노 2세대 공정이 기존 4나노 대비 반도체 성능을 20% 향상될 수 있는 것으로 나타났다. 전력효율, 크기도 개선돼 차세대 반도체 시장 선점에 다가서고 있다.

삼성전자는 오는 6월 일본에서 열리는 세계 최고 권위의 반도체학회인 VLSI 심포지엄 2023에서 3나노 공정 특성을 공유한다. ‘새로운 MBCFET 공정을 통한 세계 최초 3나노 파운드리 플랫폼 기술’을 발표하는 자리로, 삼성전자가 개발 중인 3나노 2세대 공정 전반에 대한 내용을 공개할 계획이다.

사전 공개된 자료에 따르면 3나노 2세대 공정은 기존 4나노 공정과 견줘 속도는 22%, 전력 효율은 34% 향상된 것으로 나타났다. 반도체가 차지하는 면적(크기)은 기존 대비 21% 축소된다. ‘성능(P), 전력(P), 크기(A)’로 불리는 반도체 핵심 경쟁력 모두 상당 부분 개선되는 것이다. 반도체 공정 미세화는 PPA 개선 성과를 극대화하는 과정이다.

삼성전자가 자사 4나노 공정과 비교해 차세대 공정 역량을 공개한 건 이번이 처음이다. 지금까지 5나노 공정 대비 성능 30%, 전력 50%, 면적 35% 수준으로 개선되는 것만 알려졌다. VSLI 심포지엄에서 공개하는 내용이 가장 최신으로 삼성전자가 핀펫 구조로 양산하는 최선단과 비교했다는 점에서 의미가 있다. 4나노 공정은 10여년간 반도체 업계를 주도했던 핀펫 구조를 사용한 마지막 삼성전자 공정이다.3나노 1세대부터 차세대 트랜지스터 구조인 ‘게이트올어라운드(GAA)’를 채택했다.

삼성전자가 구체적인 3나노 2세대 공정 세부사항을 발표하는 건 기술 개발이 막바지 단계임을 시사한다. 기존 3나노 공정을 한층 고도화해 첨단 반도체 제조 경쟁력을 입증하려는 시도로 보인다.

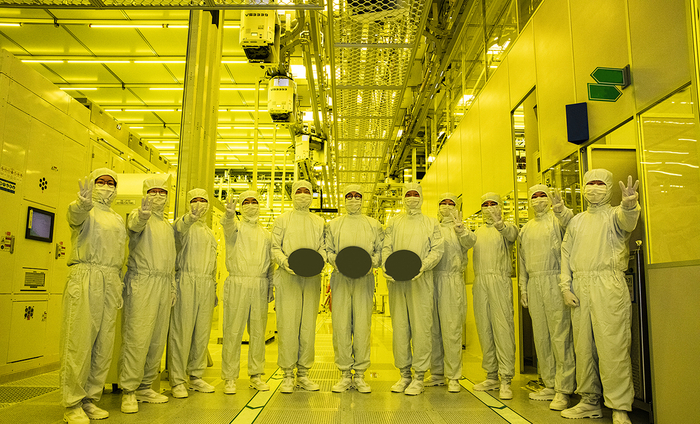

삼성전자는 지난해 세계 최초 3나노 GAA 양산에 성공했다. TSMC도 작년 말 3나노 공정에 돌입했다고 발표했지만 삼성전자와 다른 핀펫 구조를 유지했다.

삼성전자는 지난해 7월 2분기 실적 발표에서 모바일 분야에서 복수의 3나노 2세대 고객을 확보했다고 밝힌 바 있다. 퀄컴 수주 가능성이 제기된다. 퀄컴은 ‘스냅드래곤 8’ 1세대 제품을 삼성전자에 위탁생산했지만 개선제품(플러스)부터 지금까지 애플리케이션프로세서(AP) 생산을 TSMC에 맡기고 있다.

권동준 기자 djkwon@etnews.com