인텔이 첨단 반도체 패키징에 유리 기판을 도입한다. 기존 플라스틱 기판 한계를 넘어 고성능 반도체를 구현하기 위한 소재 전환 시도다. 반도체와 기판 접점 거리를 좁혀 칩 성능을 높이는 기술도 개발, 차세대 제품에 확대 적용할 방침이다.

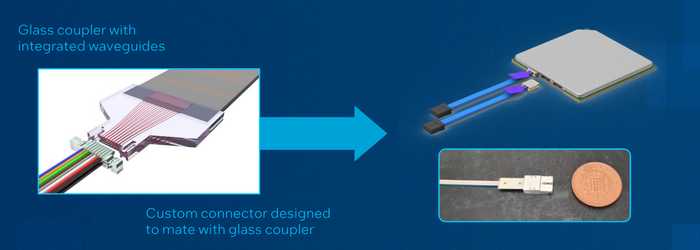

인텔은 최근 ‘인텔 첨단 패키 라운드테이블’ 간담회를 열고 유리 기판 도입 계획을 밝혔다. 2020년대 말 도입 예정이라고 언급했다. 최소 5~6년 안에 반도체 기판 소재에 대대적인 변화가 예상된다. 푸야 타다욘 인텔 펠로우는 “반도체 부착 기판을 유리 재질로 바꿀 것”이라며 “전력 소모를 절감하는 등 강점이 있다”고 밝혔다.

반도체 기판은 반도체 칩과 컴퓨터 메인보드를 연결하기 위한 부품으로 보통 칩 아래에 부착한다. 기존에는 플라스틱 계열 소재로 만든 기판을 사용해왔다. 플라스틱은 형태를 만들기 쉽고 가격이 저렴해 패키징 기판 대세로 자리잡았다. 그러나 패키징 시장에서도 반도체 회로 설계처럼 미세 공정이 요구되면서 한계에 직면했다. 플라스틱 기판은 표면이 거칠고 두께를 줄이는데 어려움이 있기 때문이다. 패키징 크기가 커지면서 기판이 휘는 문제도 발생하고 있다.

반면 유리 기판은 표면이 평탄하고 매우 얇게 만들 수 있다. 플라스틱과 견줘 절반 정도 두께로 줄일 수 있다. 두께가 줄면 신호 전달 속도와 전력 효율성을 높일 수 있다. 이를 통해 기존 대비 40% 가량 반도체 칩 성능 개선이 가능한 것으로 알려졌다.

특히 두께는 3차원(3D) 패키징이 확산되면서 더욱 주목받는 요소다. 반도체를 수직으로 쌓아 성능을 높이려는 시도가 잇따르는데 이를 위해서는 기판 두께를 줄이는 것이 관건이다. 반도체가 차지하는 공간을 최소화하기 위해서다. 인텔은 유리 기판을 통해 3D 패키징 구조 개선에 나설 것으로 예상된다.

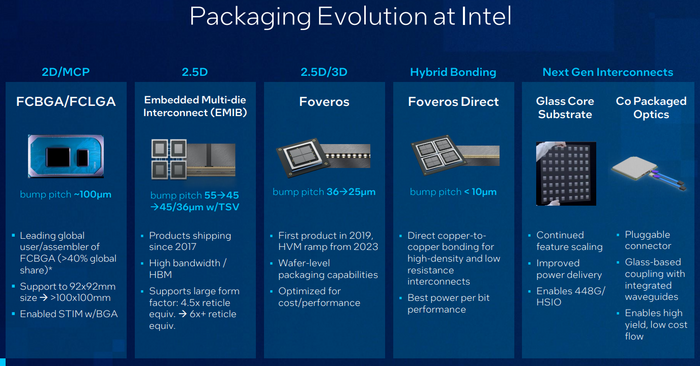

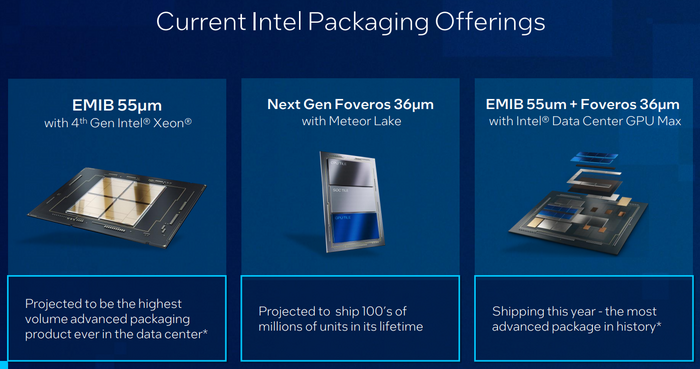

인텔은 반도체 칩과 기판의 접점 거리(범프 피치)를 줄이는 기술도 고도화하고 있다. 접점 거리가 짧아질 수록 패키징 크기가 줄어 다양한 기기에 적용할 수 있고 성능도 높일 수 있다. 인텔은 현재 범프 피치를 약 36마이크로미터(㎛) 까지 구현했다. 업계 최단거리 수준이다. 인텔은 내년에 이를 25㎛까지 줄일 계획이라고 밝혔다.

인텔은 하이브리드 본딩 기술도 준비 중이다. 인텔 포베로스 다이렉트라고 명명했다. 지금까지 반도체를 적층하거나 기판과 연결할 때 솔더볼을 사용해왔다. 하이브리드 본딩은 전기 특성이 우수한 구리와 구리를 직접 연결해 적층 간격을 축소하고 신호 전달 속도를 높이는 차세대 패키징 기술이다. 인텔은 하이브리드 본딩으로 범프 피치를 10㎛ 이하로 줄일 것으로 내다봤다. 이르면 올 하반기부터 인텔 제조 공정에 적용된다.

이같은 행보는 점점 어려워지는 반도체 회로 미세화 한계를 패키징으로 이겨내려는 복안이다. 최근 반도체 업계는 회로 선폭을 줄이는 전공정이 아닌 패키징 등 후공정 분야 기술로 반도체 성능을 높이는데 주력하고 있다. 이를 통해 2년마다 반도체 집적도가 2배 높아진다는 ‘무어의 법칙’을 유지하는 것이 목표다. 인텔은 “무어의 법칙을 이끄는 핵심 분야 중 첨단 패키징 기술이 매우 중요한 역할을 하게 됐다”고 밝혔다.

권동준 기자 djkwon@etnews.com