바야흐로 패키징의 시대다. 인공지능(AI) 데이터를 연산할 반도체가 필수가 됐지만, 기존 회로 미세화 전략으로는 시장이 요구하는 성능을 맞추기 어려워졌다. 반도체 업계에서는 이같은 상황을 타개하기 위한 '첨단 패키징'에 주목하고 있다.

수평 구조였던 반도체 패키지가 2.5 및 3차원(D) 등 수직 적층으로 진화하는 것이 대표적이다. 서로 다른 반도체를 연결, 성능을 극대화한 '칩렛' 기술에 대한 연구개발(R&D)도 한창이다. 반도체 성능을 고도화하기 위한 새로운 접근법이다.

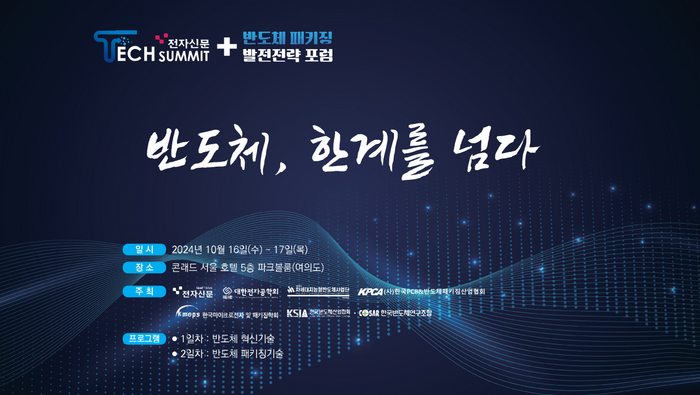

전자신문과 반도체 패키징 발전전략 포럼이 공동으로 주최, 16~17일 서울 여의도 콘래드호텔에서 열리는 '반도체 한계를 넘다' 콘퍼런스는 둘째날부터 반도체 패키징 기술을 다룬다. 반도체 제조사부터 소재·부품·장비(소부장), 주요 연구기관 등 생태계 주체가 첨단 패키징 발전 전략을 논의한다.

문기일 SK하이닉스 부사장은 'AI 시대 도래에 따른 패키징의 기술적 가치'에 대해 발표한다. 반도체 칩을 보호하고 동작시켰던 과거 역할을 넘어 시스템 구현과 성능을 좌우할 핵심 요소로 거듭난 패키징을 집중적으로 다룰 예정이다.

특히 AI 메모리로 급부상한 고대역폭메모리(HBM)의 성능을 담보하는 패키징 혁신 기술에 대해 논의한다. SK하이닉스는 AI 반도체 칩에 공급되는 HBM 시장 점유율 1위다.

문 부사장은 AI 시대에 필요한 시스템온패키징(SiP) 기술과 이를 위한 소재·부품·장비(소부장) 협업 필요성도 강조할 계획이다. 반도체 경쟁력을 극대화할 균형 잡힌 산업 생태계 조성 전략도 제시한다.

대규모 예산을 투입, 우리나라 반도체 패키징 경쟁력을 끌어올릴 연구개발(R&D) 사업에 대한 청사진도 제시된다. 이정호 한국산업기술기획평가원(Keit) PD는 '반도체 첨단 패키징 선도 기술 개발 사업'에 대한 로드맵을 공유할 예정이다.

사업은 산업통상자원부가 패키징 산업 경쟁력을 위해 추진한 것으로 지난 6월 예비타당성조사(예타)를 통과했다. 2031년까지 약 7년간 2744억원을 투입할 예정이다. 첨단 패키징 초격차 선도 기술을 개발하고 반도체 소부장 및 후공정 기업(OSAT)의 핵심 기술 확보, 글로벌 패키징 연구 협력 체계 구축 등이 골자다.

첨단 패키징 기술 우위를 확보하려는 미국·일본·대만 등 국가별 경쟁이 치열한 가운데, 우리나라 R&D 사업의 구체적인 방향을 확인할 수 있는 기회다.

과학기술정보통신부에서 2029년까지 495억원을 투입해 구축하는 반도체 첨단 패키징 인프라 구축 지원 사업도 면밀히 살필 수 있다. 사업은 12인치 웨이퍼 기반 첨단 패키징 장비와 공정 환경을 갖춘 공공 파운드리를 구축, 국내 팹리스·OSAT·소부장 기업·연구기관 및 대학에 개방형 R&D 서비스를 제공하는 게 목표다. 주관기관인 나노종합기술원 오재섭 실장이 첨단 패키징 분야 소부장 국산화와 차세대 패키징 R&D를 지원하기 위한 사업 전반을 다룰 예정이다.

유문상 심텍 연구개발그룹장(이사)은 반도체 성능 고도화를 위한 필수 요소인 '차세대 기판 기술' 전략을 제시한다. 시스템 반도체 뿐 아니라 메모리까지 회로 미세화에 따른 패키징 변화가 요구된다. 보다 많은 데이터를 주고 받기 위한 반도체 입출력(I/O) 증가가 트렌드로 자리잡으면서 대대적인 기판 변화가 불가피해졌다.

유 그룹장은 패키징 핵심 소재인 프리프레그를 활용한 '플립칩-볼그리드어레이(FC-BGA)' 기판 기술의 강점과 양산 현황을 소개한다. FC-BGA는 고부가가치용 반도체 기판으로, AI 등 고성능컴퓨팅(HPC) 시장을 위해 기판 업체들이 앞다퉈 양산 능력을 확보하고 있다.

이번 행사는 누구나 참석이 가능하며, 행사에 대한 자세한 내용은 전자신문 홈페이지 콘퍼런스 메뉴에서 확인할 수 있다.

권동준 기자 djkwon@etnews.com