어플라이드머티어리얼즈가 2나노미터(㎚) 이하 초미세 회로 구현이 가능한 반도체 소재와 공정 기술을 개발했다. 반도체 미세화 한계를 극복하는 기반이 될 지 관심이 쏠린다.

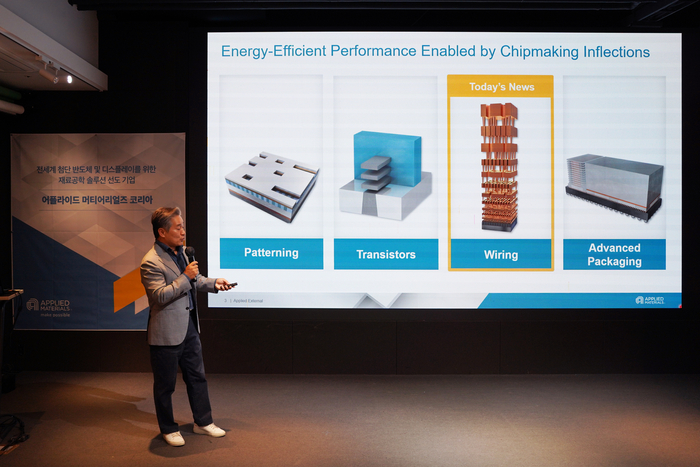

어플라이드는 14일 2㎚ 이하 반도체에서 초박막 금속 배선을 구현할 수 있는 기술을 공개했다. 구리 금속 배선에 '루테늄'을 적용한 것이 특징이다.

금속 배선은 전기적 신호를 전달하는 길을 만드는 것이다. 특히 저항이 낮은 구리를 많이 활용한다. 첨단 시스템 반도체 칩에는 96㎞ 이상되는 미세 구리가 배치돼 있다.

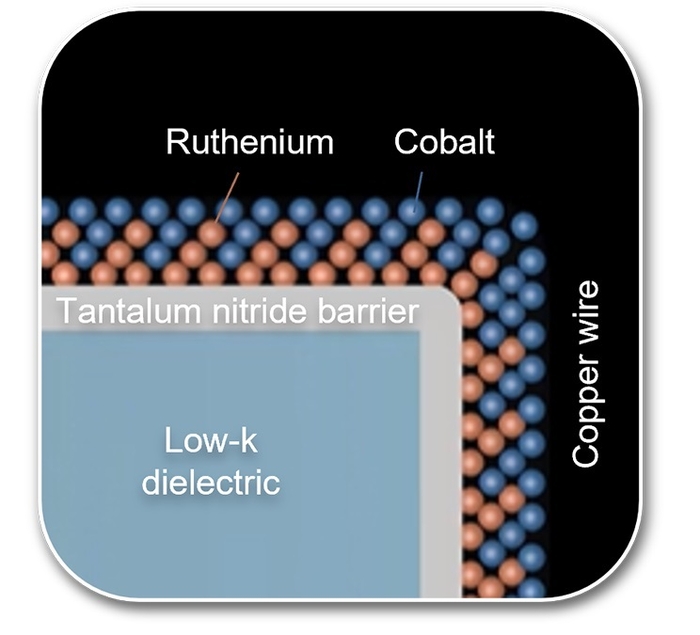

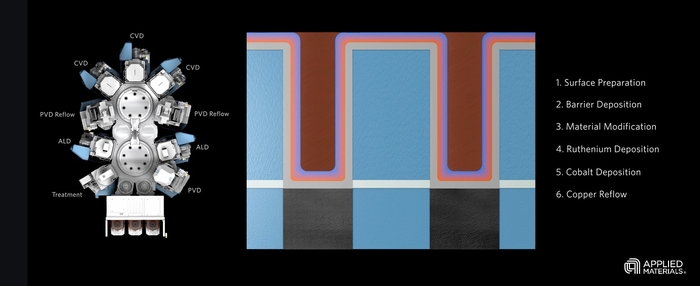

반도체 내에 구리선을 구축하려면 '배리어'와 '라이너'라는 층이 필요하다. 베리어는 구리가 칩에 유입돼 수율을 낮추는 것을 방지하고, 라이너는 이 배리어가 안정적으로 접착되도록 코팅하는 역할이다. 베리어와 라이너 층이 얇을수록 많은 양의 구리선을 안정적으로 배선할 수 있다.

배리어와 라이너 층 두께를 줄이는 건 업계 난제로 손꼽힌다. 반도체 회로는 수㎚ 수준으로 줄었지만, 소재 문제로 배리어와 라이너 층 축소는 어려워서다. 저항값을 높이는 원인이 됐다.

어플라이드는 라이너 층에 루테늄 원소를 새롭게 적용해 두께를 최대 33% 줄이는데 성공했다고 밝혔다. 기존 라이너는 코발트만 써왔는데, 루테늄까지 함께 쓰는 '이원 금속 조합' 방식을 통해 이를 구현했다. 루테늄 필요성은 지금까지 학계에서 강조해왔지만 실제 상용화한 건 어플라이드가 처음이다.

이은기 어플라이드 박막기술 총괄은 “보다 미세한 라이너막을 형성해 반도체 성능에 영향을 미치는 구리 배선 저항값을 낮췄다”며 “이를 통해 반도체 성능과 전력 효율을 높일 수 있게 됐다”고 밝혔다.

어플라이드에 따르면 구리 배선에 루테늄을 적용했을 때 저항값은 25% 줄고, 전력 효율은 25% 증가하는 것으로 나타났다.

어플라이드는 이 기술을 바탕으로 공정 장비도 개발했다. 루테늄을 쓸 수 있는 장비(엔듀라 쿠퍼 배리어 시드 IMS)로, 구리 배선을 위한 화학기상증착(CVD)·물리적기상증착(PVD)·원자층증착(ALD) 등의 공정을 모두 수행할 수 있다고 설명했다.

어플라이드는 2나노 이하 초미세 회로에 루테늄 기술이 활용될 것으로 전망했다. 이미 삼성전자와 TSMC의 3㎚ 시스템 반도체 대량 생산에 투입, 양산에 성공하면서 기술력을 검증 받았다. 삼성전자와 TSMC 모두 2㎚ 양산을 준비하고 있어 도입 범위가 확대될지 주목된다.

어플라이드는 이날 구리 배선 간 신호 전달 속도를 높이는 신기술도 공개됐다. 차세대 저유전율(로우 K) 박막으로 구리 배선을 감싸는 방식이다. 신호 속도를 높이려면 반도체 내부에 전하 축적(정전용량)을 낮춰야 한다. 축적 전하가 구리선 간 신호 간섭을 야기해서다. 어플라이드 저유전율 박막은 전하 축적을 방지하고 물리적 강도도 높여, 반도체의 3차원(3D) 수직 적층도 가능하다고 회사 측은 부연했다.

권동준 기자 djkwon@etnews.com