케이던스가 업계 최초로 Arm과 협력한 칩렛 기술을 공개했다. 칩렛은 서로 다른 반도체(다이)를 연결, 미세화 한계를 극복할 차세대 첨단 패키징 기술로 손꼽힌다. 최근 설계부터 칩렛 기반으로 반도체 개발이 추진되고 있다.

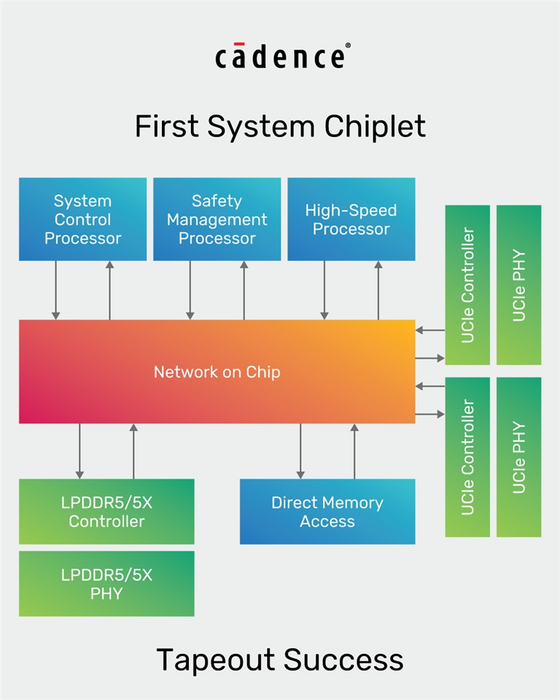

케이던스는 최근 개발한 칩렛 기술로 프로세서와 시스템 반도체, 메모리 설계자산(IP)을 단일 패키지에 통합, 시제품 제작 및 테이프 아웃까지 완료했다고 밝혔다.

신규 칩렛 기술은 Arm의 '칩렛 시스템 아키텍처(CSA)' 기반으로 설계됐다. 테이프아웃은 칩 설계를 완료해 제조 공정에 넘기는 단계로 실제 양산 가능한 수준의 기술을 확보한 것으로 풀이된다.

또 '유니버셜 칩렛 인터커넥트 익스프레스(UCIe)'를 통해 반도체 IP를 상호 연결했다. UCIe는 칩렛 시장에 대응하기 위해 주요 업체들이 참여하는 표준 인터페이스 규격이다. 보다 많은 반도체 개발업체가 활용할 수 있도록 표준 생태계에 대응한 것이다. 고객이 제품의 시장 출시 기간을 단축하는 데 초점을 맞춰 단순한 설계 구조를 구현했다.

양사는 지난 3월부터 케이던스의 IP와 설계자동화(EDA) 솔루션에 Arm의 IP 기술을 결합, 시스템 칩렛을 개발해 왔다.

케이던스는 기존 칩 설계가 기존 단일 실리콘 온 칩(SoC) 형태에서 칩렛으로 전환될 것으로 전망했다. 반도체 별로 생산 공정을 다르게 해 비용을 줄일 뿐 아니라 수율을 높일 수 있어서다. 반도체 경쟁력을 좌우하는 전력·성능·면적(PPA) 측면에서도 칩렛이 유리한 것으로 알려졌다.

박진형 기자 jin@etnews.com