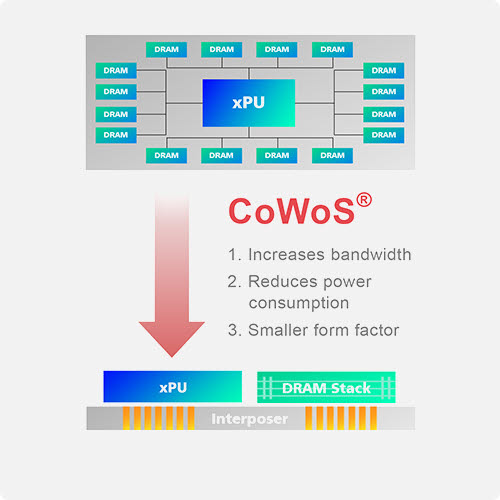

대만 파운드리 업체 TSMC가 차세대 패키징 '칩-온-웨이퍼-온-서브스트레이트(CoWoS)' 기술을 업그레이드했다. CoWoS는 인쇄회로기판(PCB) 대신 인터포저라는 판 위에 메모리와 로직 반도체를 올리는 패키징이다. 기존 패키징보다 실장 면적이 줄고, 칩 간 연결을 빠르게 할 수 있어 고성능컴퓨팅(HPC) 업계에서 각광받는다.

TSMC는 최근 차세대 패키징 기술인 CoWoS를 한층 발전시켜 고객사 칩 양산에 적용했다고 밝혔다. 이 기술은 미국 통신 칩 업체 브로드컴 집적 회로 패키징에 활용된다.

패키징은 가공이 끝난 실리콘 웨이퍼에서 자른 칩을 포장하는 작업이다. 각종 불순물과 충격으로부터 칩을 보호하고 메인 보드와 신호를 원활하게 교류할 수 있도록 배선을 재배열하는 공정이다.

TSMC의 패키징 기술 중 하나인 CoWoS는 2012년 소개된 이후 꾸준히 발전하고 있다.

통상 반도체를 패키징할 때는 완성된 다이에 인쇄회로기판(PCB)을 칩 아래에 장착해 재배선(RDL) 과정을 거친다. 그러나 CoWoS는 메모리와 로직반도체를 실리콘 기반 '인터포저'라는 판에 한 번에 올리는 방법을 쓴다. 인터포저 위에는 메모리와 로직 반도체를 평면으로 놓기도 하고, 수직으로 쌓기도 한다. 2D와 3D가 합쳐진 형태라 '2.5D' 패키징이라고도 부른다.

CoWoS는 반도체 간 거리가 가까워져 실장 면적이 줄고, 칩 사이 연결이 빨라질 수 있도록 많은 양의 배선을 설치할 수 있다는 장점이 있다.

기술이 발전하면서 인터포저 크기도 늘어나고 있다. 2012년 TSMC가 처음으로 이 기술을 소개했을 때 인터포저 면적은 800㎟에 불과했다. 그러나 이날 발표한 인터포저 면적은 1700㎟나 된다. 약 8년 새 면적이 2배 이상 늘어나, 더 많은 칩을 올릴 수 있게 된 것이다. 또 초기에는 28나노 칩에 대응할 수 있는 기술로 출발했지만 이제는 5나노 칩도 대응할 수 있다.

TSMC 측은 “새로운 CoWoS 기술은 2개 로직 시스템온칩(SoC) 다이와, 96GB 고대역폭(HBM) 메모리 6개를 올릴 수 있다”며 “이 공법은 초당 2.7테라바이트 대역폭을 제공하는데, 2016년 TSMC가 가지고 있던 CoWoS 솔루션보다 2.7배 빨라진 것”이라고 밝혔다.

메모리와 로직 반도체 간 연결성을 극대화한 이 기술은 고성능 컴퓨팅 시스템 업계에서 주목받을 것으로 예상된다. TSMC는 메모리 칩이 유용하게 쓰이는 딥러닝, 5G 네트워크 인프라, 데이터센터 업계 등에서 이 기술이 각광받을 것으로 예상했다.

TSMC는 CoWoS와 함께 통합팬아웃(InFO) 기술로 패키징 기술 확장을 노리고 있다. 칩의 배선을 밖으로 빼내서 패키징을 하는 기술인데, 2016년부터 애플 칩의 팬아웃 패키징을 싹쓸이 하면서 패키징 업계 주도권을 잡은 바 있다.

삼성전자도 인터포저를 이용한 패키징 기술 상용화에 박차를 가하고 있다. 스마트폰 카메라 이미지센서 뒤에 장착하는 메모리와 로직 반도체를 한 번에 얹는 작업을 칩-온-웨이퍼 기술로 구현하는 것으로 전해진다.

한 업계 관계자는 “이 기술과 관련된 삼성전자의 외주 고객사가 아직 많지는 않은 것으로 알고 있다”고 밝혔다.

강해령기자 kang@etnews.com