차세대 반도체 소자 연구에서 전력 효율성을 극대화하는 핵심 원천 기술을 국내 연구진이 개발돼 주목받고 있다.

9일 업계에 따르면 한국과학기술원(KAIST) 조병진 교수팀은 게르마늄(Ge) 웨이퍼 위에 새로운 콘셉트의 절연막을 만들어 누설 전류를 최소화하는 신기술을 개발했다.

오늘날 반도체 기술은 '입체화'에 초점이 맞춰져 있다. 시장에서 자주 언급되는 핀펫, 게이트올어라운드(GAA) 같은 최신 공정은 소자 입체화로 크기를 줄여 원가절감과 성능향상을 동시에 모색할 수 있다는 장점이 있다.

문제는 크기가 줄면서 전자와 홀의 이동이 느려진다는 점이다. 이는 칩 동작 속도 저하와 연결돼 미세화의 한계로 지적돼 왔다.

학계에서는 이를 극복하기 위해 다양한 연구를 진행 중이다. 한 예로 차세대 소자에서는 실리콘 웨이퍼보다 전자와 홀의 이동속도가 더 빠른 Ge 기반 웨이퍼로 소자를 만드는 연구가 있다.

조병진 교수팀은 Ge 기반 웨이퍼에서 기능이 극대화한 절연막을 만드는 원천 기술을 개발했다.

반도체 내에는 일정 구간에서 전자의 이동을 통제하기 위한 절연막으로 산화막을 만든다.

산화막은 칩 미세화가 진행되면서 균일하면서 얇게 씌워져야 하는 숙제를 안고 있는데, 특히 Ge 웨이퍼 소자에서는 양질의 절연막 형성이 쉽지 않아 전력 누설이 문제가 됐다.

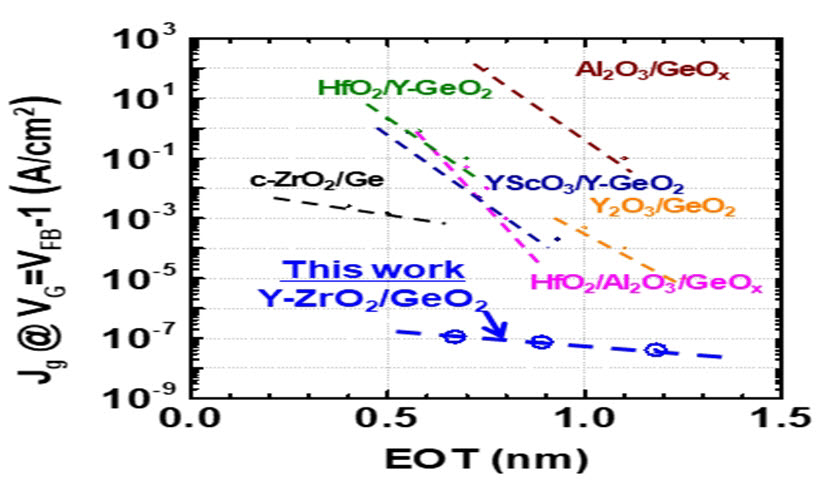

조 교수는 Ge 반도체에 기존의 산화막 대신 이트륨(Y)이 도핑된 지르코늄 산화막(ZrO2)을 형성했다.

매우 높은 압력의 수소 분위기에서 열처리를 하면서 절연막의 누설전류를 크게 줄이고 계면특성을 크게 향상시켰다. 조 교수는 “기존 기술에 비해 칩 소형화는 물론 전력소모를 감소시키고 발열을 최소화 할 수 있는 이점을 가지고 있다”고 설명했다.

안기현 반도체산업협회 상무는 “미세화 기술 한계로 기술개발의 속도가 점점 느려지고 있었는데, 이번 기술로 개발속도가 빨라져서 초격차 전략에 속도를 낼 수 있을 것”이라고 말했다.

이 기술로 조 교수 연구진은 '제26회 한국반도체학술대회 최우수논문상을 수상하기도 했다.

한편 이번 연구는 산업통상자원부와 삼성전자, SK하이닉스에서 지원하고 있는 '미래반도체소자 원천기술개발사업' 지원으로 개발됐다. 정부와 산업계가 공동으로 운영하는 이 사업은 미래반도체 원천기술개발과 연구인력 양성을 목표로 학계 연구개발을 지원한다. 2013년 출범해 현재 4~7기를 운영 중이다.

강해령기자 kang@etnews.com