국내 연구진이 최첨단 반도체 개발 키를 쥔 '패키징' 분야 핵심원천 신소재 기술개발에 성공했다. 반도체강국 신화를 계속 써 나가는 AI 반도체 제조 핵심 소재기술로 사용될 전망이다.

한국전자통신연구원(ETRI)은 자체 보유 나노 소재기술로 반도체 공정에 꼭 필요한 신소재를 개발했다.

그동안 반도체 업계는 첨단 반도체 패키징 공정에 일본 소재를 사용해 왔다. 또 공정이 9단계에 달하고 높은 전력소모, 청정실 유지비용, 유해물질 배출 등 문제도 있었다.

연구진은 자체 보유 나노소재 설계기술과 신소재를 활용해 20여년 연구 끝에 성과를 냈다. 기존 일본기술 대비 95% 전력 절감이 가능한 획기적인 반도체 칩렛 패키징 기술이다.

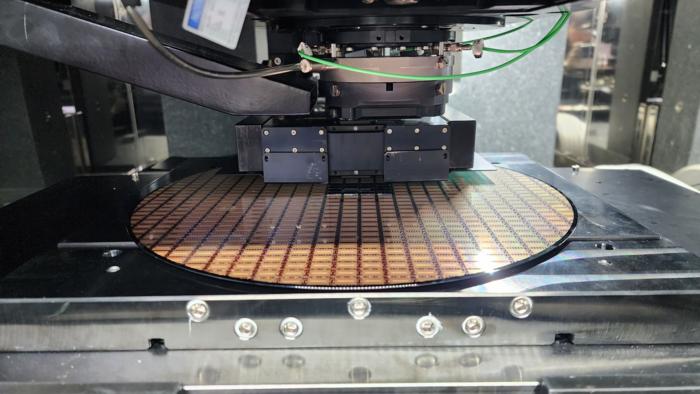

공정도 3단계로 대폭 줄였다. 개발 신소재를 웨이퍼 기판에 붙인 후 칩렛으로 타일을 만들어 면 레이저를 조사해 접합공정을 완성하고 후경화하는 총 3단계다.

고분자 필름으로 핵심 신소재를 만들었다. 10~20마이크로미터(㎛) 두께 에폭시 계열 소재에 환원제 등을 첨가했다. 이 소재에 레이저를 쏘면 반도체 후공정 단계에서 세척·건조·도포·경화 등에 이르는 전 단계를 해결할 수 있다. 칩렛을 웨이퍼 기판에 마치 타일을 붙이듯 직접 찍어 붙이는 것도 가능하다.

공정이 간단해지면서 전체 생산라인도 기존 20m 이상을 4m로 줄일 수 있다. 질소 가스도 필요 없어 유해물질도 발생하지 않는다.

첨단 칩렛 패키지에 적용할 수 있는 고정밀 공정이라는 특징도 있다. 세계 최초로 상온(25℃)에서 집적 공정이 가능하다.

연구진은 세계적인 파운드리 회사가 이번 기술 공정성·신뢰성을 평가하는 중으로, 우수 평가시 3년 내 상용화가 가능할 전망이라고 밝혔다.

ETRI 이일민 창의원천연구본부장은 “최근 ESG 경영이 반도체 디스플레이 업계 화두로, 산업계 친화적인 저전력 신공법을 누가 먼저 개발하느냐는 사활이 걸린 문제”라며 “이번 기술 파급효과가 매우 클 것”이라고 말했다.

최광성 ETRI 실장은 “그동안 첨단 반도체 패키징과 마이크로 LED 디스플레이 분야는 일본 소재와 장비 기술 의존도가 높았다”며 “기술 격차가 커 자립화가 쉽지 않는 상황이었는데 저전력·친환경이라는 시장 요구에 연구진 성과가 답해 원천기술 상용화가 기대된다”고 밝혔다.

김영준 기자 kyj85@etnews.com