삼성전자가 지난 2001년 초미세 회로 선폭의 한계인 0.10마이크로미터(㎛) 공정을 적용한 4기가 D램 제조기술을 공개했을 때 세계 반도체 업체들은 경악을 금치 못했다. 1992년 8월 64메가 D램을 세계 처음 개발한 이후 256메가(1994년 8월), 1기가(1996년 10월), 4기가 D램에 이어 세계 최초·최고 기록을 또 한 번 갈아치운 것이다. 특히 당시만 해도 초미세 회로 선폭의 한계로 여겨졌던 0.10㎛에 도달한 삼성전자는 이 공정 기술을 기존 제품에 적용하면 원가를 획기적으로 낮출 수 있다고 밝혔다. 이는 세계 반도체 제조기술 역사에 한 획을 긋는 사건으로 받아들여졌다. 1983년 삼성전자가 최초로 64킬로바이트 D램을 개발한 이래 우리나라는 대기업 주도로 대규모 연구개발 투자에 집중했다. 갈수록 해외 선발국가와의 기술격차를 좁혀온 결과 지난 1990년대 16메가 D램부터는 신제품 개발에서 해외 경쟁사들을 압도해 나가기 시작했다. 삼성전자의 0.10㎛ 공정 개발은 우리나라 반도체 산업이 해외 선발 업체들과의 기술 격차를 더욱 벌리고 기술과 원가 경쟁에서 확고한 우위를 차지하는 발판을 만들었다.

◇세상을 놀라게 하다=삼성전자는 지난 2001년 2월 7일(현지시각) 미국 샌프란시스코 국제반도체학회(ISSCC)에서 0.10㎛ 초미세 공정 기술을 적용해 시제품 단계로 개발한 `차세대 4기가 메모리 반도체 제품 기술`을 공개했다. 세계 최초로 0.10㎛ 초미세 공정 기술과 4기가 제품의 제조 기술을 확보한 개가였다. 당시 반도체 업계가 가격 경쟁 격화로 원가 절감에 골몰하고 있던 상황에서 차세대 반도체 시장을 겨냥한 새로운 공정 기술이 탄생하는 순간이었다.

반도체 제조 원가를 낮추는 가장 좋은 방법은 생산성 향상이다. 웨이퍼 투입량 대비 생산량을 늘리는 방법이다. 여기에는 더욱 세밀하게 설계해 한 장의 웨이퍼로 많은 칩을 만드는 초미세회로 기술과 웨이퍼 자체를 크게 하는 기술 두 가지가 있다.

당시 인텔·TI·AMD·TSMC 등 주요 반도체 회사들은 0.18㎛ 초미세회로 설계 기술을 양산 라인에 적용한 데 이어 0.15㎛와 0.13㎛ 설계 기술 도입을 놓고 경쟁하는 상황이었다. 어느 회사가 먼저 초미세 공정 기술을 안정화시키는지에 따라 수익성은 크게 달라진다. 당시 반도체 회사들은 저마다 노하우를 축적해 공정기술을 0.13㎛까지 미세화하는 데 성공했지만 낮은 수율로 상용화가 어려웠다.

웨이퍼를 키우는 방법은 막대한 투자비가 부담이었다. 많은 반도체 업체가 300㎜ 웨이퍼 공정의 설비 투자를 선언했으나 2000년 말에 닥친 불황으로 회사마다 채산성이 악화돼 투자여력이 없었다. 특히 대만의 D램 업체들은 현지 경제 위기에 따른 자금 시장 악화로 300㎜ 웨이퍼 투자를 엄두도 내지 못했다. 웨이퍼 공장을 가동한다 해도 적절한 수율이 나올지 장담할 수 없는 상황이었다. 이런 치열한 경쟁 속에서 삼성전자의 0.10㎛ 초미세 공정 기술 확보는 세계 D램 업계에 큰 충격을 줬다. 이 기술을 기존 양산 라인에 적용하면 D램 제조원가를 획기적으로 낮출 수 있어 삼성전자와 도저히 경쟁할 수 없기 때문이다. 0.10㎛ 초미세 공정을 삼성전자가 당시 생산했던 128메가와 256메가 D램 라인에 도입하면 60% 이상의 원가절감 효과가 있을 것으로 예상됐다. 삼성전자 관계자는 “0.10㎛ 기술은 당시 0.18㎛ 기술에 비해 생산성이 두 배 이상이었다”며 “반도체 값이 계속 떨어지더라도 수익성을 맞출 수 있었다”고 설명했다.

◇미세 공정 기술만 얻은 것이 아니다=삼성전자는 반도체 재료인 실리콘 웨이퍼와 광원인 불화크립톤(KrF)을 사용해 0.10㎛ 공정 기술을 개발했다. 이 과정에서 4기가 D램에 0.10㎛의 초미세 회로 선폭을 구현하는 각종 공정기술과 이득조절감지(GCP:Gain Controlled Pre-Sensing) 기술을 이용한 미세 증폭 회로 등의 설계 기술도 확보했다. 고해상도 사진 현상, 셀 정전용량 확보, 저저항 배선 등 핵심 기술을 섭렵해 실리콘 웨이퍼와 KrF로 구현할 수 있는 기술의 한계인 0.10㎛에 도달한 것이다. 삼성전자는 미세 증폭 회로 기술을 비롯해 △비트라인 자기보정(RBC:Reference Bit-Line Calibration) 기술을 적용한 안정화 회로 △저전압 및 공정 변동에 대응하는 설계 기술 등에서 획기적인 진보를 이룰 수 있었다. 0.10㎛ 공정기술로 개발한 4기가 D램은 42억9000만비트 용량으로 하나의 칩에 영문자 기준 5억자(신문 3만2000페이지) 이상, 단행본 640권, 정지영상 1600장, 64시간 분량의 음성데이터를 저장할 수 있었다.

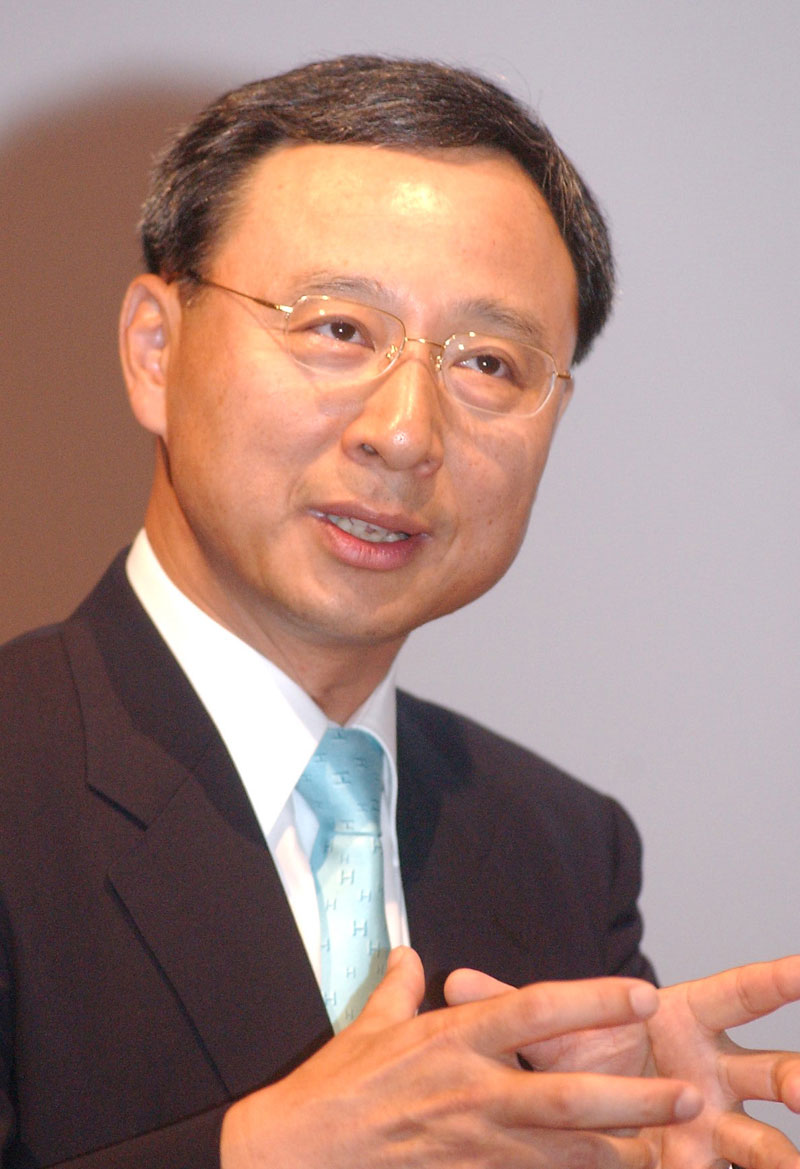

◇반도체 시장에서 입지를 굳히다=삼성전자는 4기가 제품 개발로 D램 시장에서 우월적 지위를 굳혔다. 특히 양산 직전 시제품 단계로 개발한 D램은 바로 샘플로 공급할 정도의 기술력을 확보한 상태였다. 황창규 당시 삼성전자 메모리반도체부문 사장은 “반도체를 둘러싼 시장과 기술 환경은 늘 급변하기 때문에 항상 차세대 제품을 준비해야 한다”고 말했다. 당시는 경쟁사들이 1기가 제품과 0.13㎛ 공정기술을 개발하던 상황이었다. 삼성전자의 4기가 D램 기술 개발은 통상 6개월로 인정되던 삼성전자와 해외 업체 간의 기술격차가 1년 이상 벌어졌다는 평가를 받았다. 또 차세대 기가 반도체 제조에 대한 140여 건의 원천 특허를 출원해 막대한 로열티 수입도 거둬들였다. 특히 삼성전자가 집중 육성하는 시스템온칩(SoC:메모리·논리회로 등을 하나로 집약시킨 칩) 사업에서도 확실한 주도권을 갖게 됐다. 황 전 사장은 “삼성전자 4기가 D램에는 0.10㎛ 기술 등 공정 기술과 다양한 설계 기술이 거의 다 망라돼 우리나라 메모리 반도체 산업의 경쟁력을 한층 높인 계기가 됐다”면서 “이들 핵심 기술의 일부를 기존 D램에 적용해 원가경쟁력을 높일 수 있었다”고 밝혔다.

업계에서는 삼성전자가 지난 1992년 64메가 D램 개발로 기술 선두에 올라선 이래 4기가 D램 기술 개발을 정점으로 10년 넘게 선두 자리를 지켰다는 점을 높게 샀다. 업계 관계자는 “급변하는 시장 환경의 변화에서 한 기업이 5년 이상 1위를 지킨다는 것은 드문 일”이라며 “4기가 D램 기술 개발은 삼성전자가 미래에도 반도체 시장을 선도할 수 있음을 보여준 것”으로 평가했다. 황 전 사장은 “이 같은 성과는 어려운 상황에서도 묵묵히 연구해 온 개발팀의 공로”라며 “4기가 D램 개발에 만족하지 않고 차세대 기술 개발과 원가 혁신에 집중하겠다”고 다짐했었다. 삼성전자는 당초 예정에 맞춰 지난 2003년 1월 세계 최초로 0.10㎛ 공정 기술로 개발한 4기가 더블 데이터 레이트(DDR) SD램 모듈을 출시하며 상용화의 길을 열었다. 당시 DDR333·DDR400 등 고속 D램 시장의 70% 이상을 점유하고 있던 삼성전자는 4기가 DDR 모듈 양산에 들어가 후발 업체와의 격차를 한층 더 벌렸다. 300㎜ 웨이퍼에 0.10㎛ 공정을 도입한 세계 최고의 기술력은 물론이고, 우리나라가 D램 시장에서 독보적인 우위를 점할 수 있는 경쟁력을 다시 한번 확인시켜준 계기였다. 강준 당시 삼성전자 메모리 상품기획팀장 전무는 “차세대 고성능 시스템에 대응할 대용량 메모리 솔루션을 모두 갖추게 됐다”며 “세계적인 컴퓨터 업체와 협력해 차세대 DDR 제품 공급 확대에 적극적으로 나설 계획”이라고 말한 바 있다.

0.10㎛ 공정기술 개발 이후 삼성전자는 2002년 90나노, 2003년 80나노, 2005년 70나노 공정 개발에 성공하고 지난 2007년에는 세계 최초로 50나노급 16기가 낸드플래시 양산에 돌입했다. 지난 2010년에는 업계 처음 30나노 공정의 4기가 모바일 D램을 개발하는 등 현재까지 세계 반도체 시장에서 독보적인 아성을 굳히고 있다.

[표] 삼성전자 D램 반도체 개발 제품들 (2001년 2월 기준)

(자료: 언론보도 취합)

윤희석기자 pioneer@etnews.com

![[100대 사건_057] 초미세 나노회로 공정 개발 <2001년 2월>](https://img.etnews.com/cms/uploadfiles/afieldfile/2012/09/11/315345_20120911175024_708_T0001_550.png)