삼성전자·SK하이닉스·마이크론 등 메모리 3강 기업이 10나노(㎚)대 D램 시대 준비에 박차를 가하고 있다. 그동안 애플리케이션프로세서(AP)·낸드 플래시에 비해 D램 미세공정 기술 개발 움직임은 지지부진했다. 메모리 치킨게임이 끝나면서 세 회사 모두 25나노에서 D램을 생산해도 충분히 수익을 낼 수 있었기 때문이다.

그러나 최근 삼성전자가 D램 공정을 25나노에서 20나노로 전환하면서 미세공정 경쟁에 다시 불이 붙었다. 낸드 플래시는 이미 10나노대 시대를 열었고, 시스템반도체도 핀펫(FinFET) 기술 덕분에 10나노대 진입을 눈앞에 두고 있다. 선두 업체 간 미세공정 기술 개발 경쟁이 치열해지면서 D램도 곧 10나노대 시대에 진입할 것으로 예상된다.

20나노까지는 신규 투자 없이 기존 설비로 충분히 가능할 것으로 보인다. 삼성전자가 이미 성공 모델을 보여줬고, SK하이닉스와 마이크론도 신규 투자 없이 20나노 공정 기술을 개발할 것으로 알려졌다.

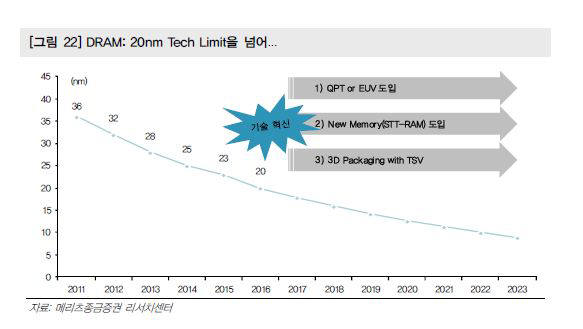

향후 D램 시장 승부처는 10나노대 진입 여부에 달려 있다. 우선 노광 기술의 한계를 넘어야 한다. 기존 더블 패터닝 기술(DPT) 노광 공정으로는 20나노가 한계다. D램 업체들은 10나노대 시대를 대비해 쿼드러플 패터닝 기술(QPT)을 준비하고 있다. 노광 공정이 늘어나지만, 기존 액침 이머전 장비를 그대로 쓸 수 있다. 장기적으로는 극자외선(EUV) 노광 기술이 도입될 것으로 예상된다.

스핀주입자화반전 메모리(STT M램) 기술이 도입되면서 기존 커패시터는 마그네틱 터널링 접합(MTJ)으로 바뀔 것으로 예측된다. D램 미세공정 기술이 고도화될수록 커패시터를 형성하기는 더욱 어려워진다. 커패시터 폭은 좁아지는데, 길이는 길어지기 때문이다. 공정 중 커패시터가 무너지면서 D램 생산 수율이 떨어진다.

STT M램은 종전 D램 공정과 95%가량 비슷해 기존 설비를 활용해 만들 수 있다. 삼성전자는 STT M램 기술을 확보하기 위해 지난 2011년 그란디스를 인수한 바 있다. SK하이닉스는 도시바와 STT M램을 공동 개발하고 있다.

실리콘관통전극(TSV)을 활용한 3차원 패키징 기술도 D램 경쟁력에 적지 않은 영향을 줄 것으로 보인다. TSV는 실리콘 웨이퍼에 10마이크로미터(㎛) 크기의 구멍을 뚫고 구리를 채워 상하 웨이퍼 간 전기적으로 연결하는 기술이다. 종전 패키지온패키징(PoP) 대비 면적이 35% 줄고, 전력 소모량은 절반 수준으로 줄어든다. 속도는 8배 이상 빨라질 것으로 기대된다.

증권가 한 애널리스트는 “D램 미세공정이 30나노대에서 20나노대로 진입하는 데 하이K 메탈게이트(HKMG)와 DPT 기술이 큰 역할을 했다”며 “10나노대 시대에는 QPT·STT M램·TSV 등 기술 여부에 따라 D램 업체 간 경쟁력이 판가름날 것”이라고 말했다.

이형수기자 goldlion2@etnews.com