SK하이닉스가 세계 2위 프로그래머블반도체(FPGA) 업체인 알테라에 차세대 고대역폭메모리2(HBM2:High Bandwidth Memory2)를 공급키로 합의했다. 초고성능 3D D램 시장에서 경쟁사보다 한발 앞서나갈 수 있는 발판을 마련했다.

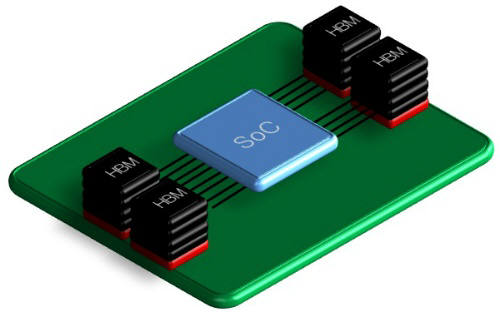

12일 업계에 따르면 알테라는 SK하이닉스 HBM2를 탑재한 프리미엄 FPGA ‘스트라틱스10 D램 SiP(System in Package)’를 2017년 출시할 계획이다. 이 제품은 기능성 패키지 기판인 인터포저(Interposer) 위로 FPGA와 D램을 나란히 얹은 것이다. HBM D램은 3D 적층 구조지만 패키지로 보면 2.5D 형태다. 스트라틱스10 D램 SiP는 데이터센터, 방송통신 네트워크, 고성능 컴퓨터 시스템용으로 고객사에 공급된다.

HBM은 D램 실리콘 다이(Die)를 수직으로 적층, 실리콘관통전극(TSV:Through Silicon Via) 기술로 연결해 대역폭을 넓힌 3D D램이다. 국제반도체표준협의기구(JEDEC)가 제정한 표준이기도 하다. 알테라는 “HBM2를 탑재한 스트라틱스10 SiP는 D램이 외부로 빠져있을 때와 비교해 메모리 대역폭이 최소 10배 늘어난다”며 “성능개선 과제였던 데이터 병목 현상을 해소하고 높은 전력 효율을 달성할 수 있을 것”이라고 설명했다.

FPGA는 주문형반도체(ASIC)와 달리 설계를 변경할 수 있어 시제품 제작에 주로 쓰였다. 그러나 최근 소프트웨어정의 인프라 환경에 대한 요구가 늘면서 상용 네트워크 제품에 FPGA를 적용하는 사례가 늘고 있다. 알테라가 FPGA에 HBM2로 성능을 높인 것도 같은 맥락이다.

SK하이닉스는 2013년 말 첫 번째 HBM을 업계 최초로 공개하며 3D D램 시장을 선점했다. JEDEC 표준화 제정 과정에서도 SK하이닉스가 주도적 역할을 한 것으로 전해졌다. 첫 HBM은 올해 출시된 AMD의 고성능 그래픽처리장치(GPU) R9 퓨리에 탑재됐다.

알테라 FPGA에 탑재되는 차세대 HBM2는 1.2볼트(V) 동작 전압에서 2Gbps 처리속도를 구현할 수 있다. 1024개 정보 입출구(I/O)로 초당 256GB 데이터 처리가 가능하다. 이는 기존 HBM(초당 128GB) 대비 두 배 빠른 속도다. 용량은 최고 4배로 늘어 8Gb D램을 4단, 혹은 8단으로 쌓을 수 있다. 엔비디아뿐만 아니라 AMD도 추후 출시할 프리미엄 GPU에 HBM2를 적용할 계획을 세웠다고 공식 밝히고 있다.

TSV를 활용한 또 다른 3D 적층 D램으로는 마이크론이 주도한 하이브리드메모리큐브(HMC) 방식이 있다. HMC는 TSV 적층 D램에 컨트롤러 기능을 하는 로직 다이가 함께 연결된 구조다. 다만 컨트롤러 기술을 보유하고 있는 대형 시스템반도체 고객사들은 순수 D램만을 적층한 HBM 방식을 선호하는 것으로 알려졌다. 삼성전자도 HMC에 역량을 쏟다가 이 같은 고객사 요구를 확인하곤 HMC2 규격 3D D램 개발을 진행하고 있다.

한주엽기자 powerusr@etnews.com