국내 반도체 패키지 업체인 네패스가 최첨단 팬아웃-패널레벨패키지(FO-PLP) 기술 사업화에 성공했다. 이번 상용화 성과는 글로벌 대기업보다 빠르게 이뤄진 것이어서 의미가 크다. 국내에선 삼성전기가 올 하반기 상용화를 목표로 PLP 기술을 개발 중이다.

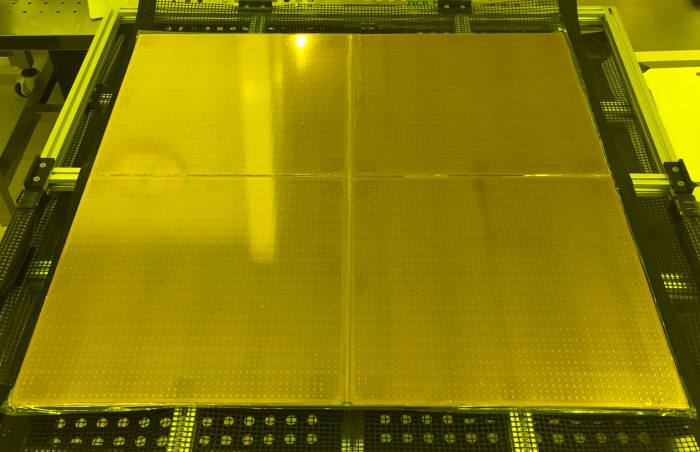

14일 업계에 따르면 네패스는 이달부터 스마트폰용 아날로그 반도체를 생산하는 D사 제품에 PLP 기술을 적용, 패키지 양산을 시작했다. 네패스는 청주2 캠퍼스의 액정표시장치(LCD) 터치스크린패널(TSP) 관련 장비를 반도체 PLP 패키지 생산용으로 전환해 양산 체제를 구축했다. 지난 수년간 비밀리에 PLP 기술을 개발해왔다.

PLP는 웨이퍼레벨패키지(WLP) 대비 생산 효율이 높다. WLP는 원형 기판 위에 가공된 웨이퍼를 잘라 칩을 올린 뒤 재배선 작업을 한다. 반면 PLP는 네모난 지지 기판 위로 칩을 올려 작업한다. 네모 형태여서 버리는 기판이 원형보다 적다. 수율을 확보하면 WLP 대비 저렴한 원가로 패키징이 가능하다.

네패스가 PLP로 패키징을 맡은 D사 제품은 기존 팬인(FI:Fan In)과 신기술인 팬아웃(FO-Fan Out)이 각각 적용돼 개별 제품으로 시장에 출하된다. 팬아웃은 입출력(I/O) 단자 배선을 바깥으로 빼 I/O를 늘리는 기술이다. 이 기술을 활용하면 I/O가 많은 고성능 칩도 저렴한 원가로 패키징할 수 있다. 패키지용 인쇄회로기판(PCB)이 필요 없어 추가 원가 절감 효과가 크다. 최종 패키지 두께도 축소할 수 있다. 팬아웃은 대만 파운드리 업체 TSMC가 최초로 상용화했다. 애플 신형 아이폰용 애플리케이션프로세서(AP)가 TSMC의 팬아웃 기술인 InFO(Intgrated Fan Out) 기술로 패키징된다.

업계 관계자는 “WLP보다 PLP가, 팬인보다 팬아웃이 기술 구현이 어렵다”면서 “두 기술을 융합해 양산한 것은 네패스가 세계 최초”라고 설명했다.

네패스는 Fo-PLP 기술로 다양한 신규 고객사를 유치하겠다는 방침을 세우고 영업을 확대하고 있다. 무선주파수(RF), 아날로그, 아날로그-디지털 혼성신호(Mixed Signal), 전력관리칩(PMIC)을 다루는 반도체 업체가 잠재 영업 대상이다.

김남철 네패스 반도체 사업부장은 “PLP는 생산 원가를 대폭 절감할 수 있다”면서 “이 기술 상용화로 패키지 시장 판도 변화가 예상된다”고 말했다.

네패스는 기존 WLP 패키지와 신규 PLP 기술을 기반으로 패키지 사업 매출을 보다 확대한다는 계획이다.

경쟁사인 삼성전기는 천안에 PLP 라인을 구축하고 양산 준비를 서두르고 있다. 초기 양산 제품은 PMIC가 될 것으로 보인다. 향후 메모리와 AP로 적용 품목을 확대해 나갈 계획이다. 본격 사업화는 내년이 될 것으로 업계에선 예상하고 있다.

한주엽 반도체 전문기자 powerusr@etnews.com