삼성전자가 7나노 극자외선(EUV) 공정으로 만든 칩을 여러 번 쌓아올려 하나의 반도체로 만드는 패키징 기술을 업계 최초로 개발했다. 평면으로 다이(die)를 배열할 때보다 반도체 크기를 줄이고, 전력 효율 향상까지 모색할 수 있게 됐다. 삼성은 이 기술을 기반으로 파운드리 사업 초격차 확보와 함께 '2030년 시스템반도체 1위' 비전 달성에 나선다.

13일 삼성전자는 3차원 적층 패키지 기술 '엑스 큐브'로 7나노 EUV 공정으로 만든 시스템반도체를 위로 쌓아 올린 테스트 칩을 생산했다고 밝혔다.

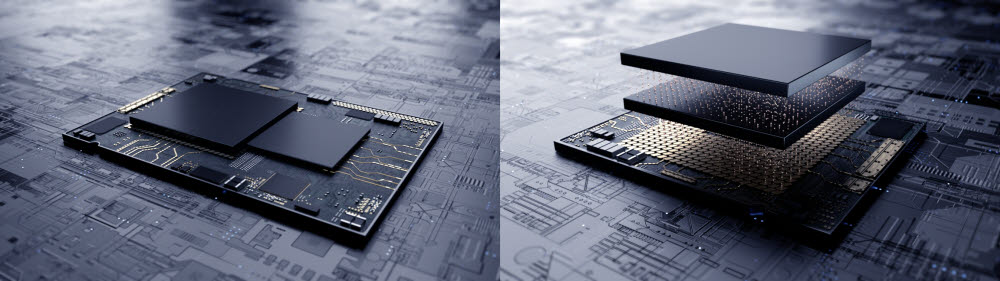

엑스 큐브는 전 공정을 마친 복수의 웨이퍼 상태 칩을 위로 얇게 적층해서 하나의 반도체로 만드는, 삼성전자의 독자 패키징 기술이다.

통상 EUV 공정으로 만든 시스템반도체는 중앙처리장치(CPU)·그래픽처리장치(GPU) 등 정보를 연산하고 처리하는 로직 부분, 반도체 안에 임시로 데이터를 저장하는 메모리 S램 부분을 하나의 칩에 평면으로 나란히 배치한다.

엑스 큐브 기술은 로직과 S램을 단독으로 설계·생산한 뒤 칩들을 위로 쌓아 올리는 방식을 구현한다. 또 적층 작업 뒤 다이 간 연결을 돕기 위해 연결선을 이용하는 대신 미세한 구멍을 뚫어 전기적 연결을 돕는 실리콘관통전극(TSV) 기술을 활용한다.

칩 적층과 더불어 전기 신호 연결 체계를 간소화하면서 전체 칩 면적 감소와 전력 효율화는 물론 데이터 처리 속도 향상까지 한꺼번에 극대화할 수 있다는 장점이 있다.

삼성의 엑스 큐브 기술은 초미세 반도체를 제조할 때 활용하는 7나노 EUV 공정으로 생산한 칩을 적층하는 최초 기술이어서 의미가 크다. 삼성전자에 위탁생산을 맡기는 글로벌 칩 설계 고객사는 삼성전자가 제공하는 엑스 큐브 설계방법론과 툴을 활용, 한층 차별화된 EUV 기술 기반의 5나노 및 7나노 첨단 칩 개발을 할 수 있게 됐다.

삼성전자는 이번 공정으로 최첨단 EUV 전 공정뿐만 아니라 패키징 기술력까지 확보, 지난해 발표한 2030년 시스템반도체 1위 비전을 달성한다는 포부다.

강문수 삼성전자 파운드리사업부 전무는 “EUV 장비가 적용된 첨단 공정에서도 TSV 기술을 안정적으로 구현해 냈다”며 “삼성전자는 반도체 성능 한계 극복을 위한 기술을 지속 혁신해 나가겠다”고 밝혔다.

강해령기자 kang@etnews.com