국내 중소 반도체 패키징 전문업체 에스앤피티가 다양한 규격의 반도체를 한 번에 패키징하는 기술을 상용화했다. 기판 하나에 한 가지 반도체만 패키징하던 기존 방식의 한계를 극복하고 개발용 반도체 칩(샘플) 제작 기간을 비약적으로 단축할 수 있게 됐다. 에스앤피티는 국내 반도체 제조사와 팹리스에 패키징 신기술을 제공하며 본격적인 사업화에 나섰다.

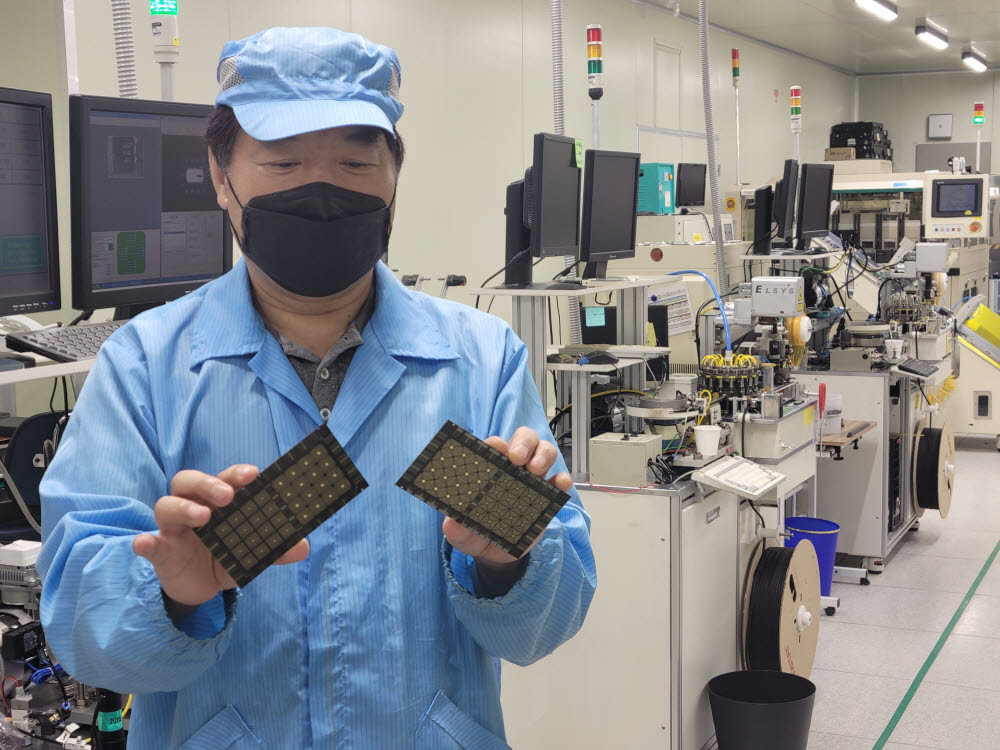

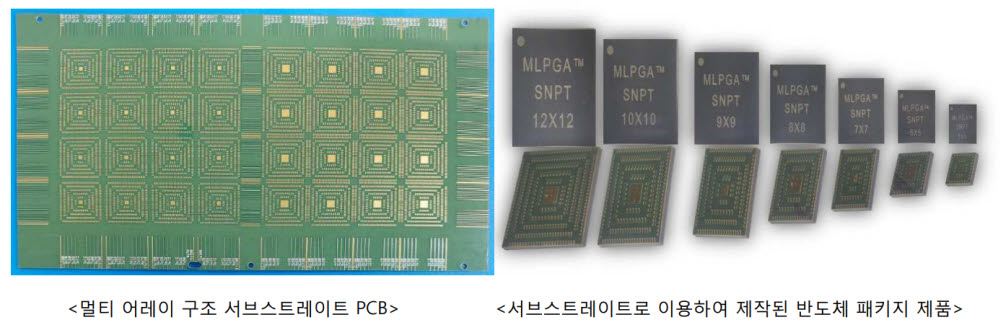

8일 업계에 따르면 에스앤피티는 다양한 규격과 크기의 반도체 패키지를 동시에 제작하는 '멀티 어레이 구조 반도체 서브스트레이트' 기술을 상용화했다.

회사는 지난 6월 특허 등록을 완료하고 국내 반도체 제조사와 팹리스 6곳의 개발용 반도체 패키징 공정에 해당 기술을 적용했다. 여러 규격의 개발용 반도체를 한 서브스트레이트에서 패키징하는 건 에스앤피티가 처음이다.

반도체 패키징 공정에서 서브스트레이트는 인쇄회로기판(PCB)과 반도체 사이에 들어가는 보조 기판이다. 웨이퍼에서 절단한 반도체(다이)를 외부와 전기적으로 연결하기 위해 사용한다. 최근 웨이퍼레벨패키징(WLP) 등 첨단 패키징 기술 등장으로 서브스트레이트 없는 패키징 기술이 떠올랐지만 여전히 시장 지배적 기술로 자리 잡고 있다. 전체 패키징 시장의 80%는 서브스트레이트를 적용하는 것으로 알려졌다.

기존에는 하나의 서브스트레이트로 한 가지 반도체 패키징만 가능했다. 예를 들어 반도체 다리(리드핀)가 사방으로 나와 있는 '4방향 표면실장 패키징'(QFP) 규격 칩과 리드핀 대신 패키지 밑면에 볼을 배치한 '볼그리드어레이'(BGA) 규격 칩을 개발하려면 2개의 서브스트레이트가 필요하다. 이 같은 방식은 서브스트레이트 소비량이 많고 패키지 제작 기간도 길어져 반도체 신제품 개발 일정을 지연시킬 수 있다.

윤희용 에스앤피티 연구소장(부사장)은 “개발용 반도체 패키징은 다품종 소량 생산이 많아 여러 서브스트레이트를 사용할 경우 샘플 제작에 4주에서 8주 정도 소요됐다”면서 “개발용 반도체 서브스트레이트의 해외 의존도도 높아 대부분 수입해야 하는 상황”이라고 밝혔다.

에스앤피티가 개발한 방식은 한 서브스트레이트 기판으로 10개 이상의 반도체 패키징 규격에 대응할 수 있다. 같은 규격에서도 기판 절단을 달리해 서로 다른 크기의 반도체 패키징이 가능하다.

이를 통해 여러 개의 샘플을 제작하는 팹리스의 칩 개발 기간을 대폭 단축할 수 있다. 여러 종류의 반도체를 동시에 제작할 수 있기 때문이다. 개발용 반도체 칩은 공급량이 100개 안팎의 소량이어서 빠르면 1~2일 안에 패키징 후 샘플 공급이 가능하다는 게 회사 측 설명이다.

에스앤피티는 반도체를 설계·개발하는 중소 팹리스, 대학 등 연구개발(R&D)용 반도체 시장을 적극 공략할 방침이다. 미국과 중국 등 해외 특허 출원도 준비하고 있다.

전태남 에스앤피티 대표는 “개발용 반도체 제작 기간을 단축하고 비용 절감 효과도 제공할 수 있어 국내 팹리스 업체의 경쟁력 강화에 기여할 수 있을 것”이라면서 “패키징 지연에 따른 신제품 개발 일정에 차질이 없도록 서비스를 제공할 계획”이라고 강조했다.

권동준기자 djkwon@etnews.com