ASML이 준비하는 차세대 노광장비인 '하이 NA 극자외선(High NA EUV)'장비가 이르면 2025년 양산될 전망이다. ASML는 하이 NA EUV 장비가 반도체 공정 비용과 개발 기간 증가라는 반도체 업계 고민을 해결할 '승부수'가 될 것이라고 자신했다.

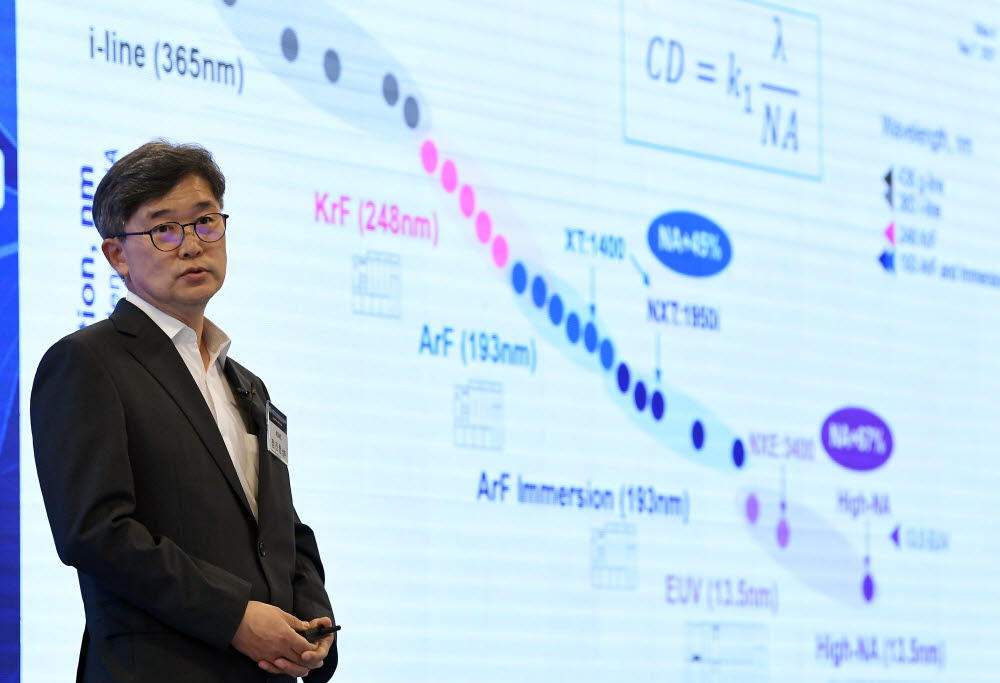

정진항 ASML코리아 상무는 테크코리아 2021에서 '하이 NA, EUV 기술의 미래' 주제 발표를 통해 차세대 EUV 노광장비 개발 현황과 기술 정보를 공유했다. 하이 NA EUV는 EUV 장비 해상력을 높여 보다 미세한 반도체 회로를 구현할 수 있는 장비로, 최근 인텔이 첨단 공정을 위해 ASML 하이 NA EUV 장비를 우선 공급받기로 하면서 업계 주목을 받고 있다. 정 상무는 “현재 하이 NA EUV 시제품 생산을 위해 개발을 진행 중”이라며 “이르면 2025년 하이 NA 장비를 양산할 수 있을 것”이라고 밝혔다.

정 상무는 반도체 제조에서 미세 공정 적용이 확대되면서 하이 NA EUV 수요가 커질 것이라고 예측했다. 그는 “하이 NA EUV는 (반도체 회로의) 싱글 패터닝 구현에 필요하다”면서 “싱글 패터닝을 반도체 공정에 적용할 경우 마스크 수를 줄여 공정을 단순화하고 시간과 비용을 줄일 수 있다”고 설명했다.

반도체 노광 공정에서 패터닝 횟수는 공정 효율화와 직결된다. 원하는 회로를 한번(싱글 패터닝)에 그릴수록 회로 패턴이 새겨진 마스크 수를 줄일 수 있어 비용을 절감하고 공정 시간을 단축한다. 최근 미세 공정으로 전환하면서 싱글 패터닝에 대한 요구가 크게 늘고 있다.

ASML EUV 장비는 10나노 이하 미세 공정도 싱글 패터닝이 가능하도록 지원한다. 그러나 반도체 공정이 보다 미세화할 경우 현재 EUV 장비도 결국 멀티 패터닝 작업을 피할 수 없을 것이란 게 정 상무 설명이다. ASML이 현재 EUV 장비의 렌즈 수차(NA)를 0.33에서 0.55까지 끌어 올린 '하이 NA' EUV를 개발하는 이유다. 정 상무는 “현재 0.33NA도 한계에 도달하면 마스크 수가 증가하는데 하이 NA(0.55)를 적용하면 다시 싱글 패터닝이 가능해 마스크 수를 줄일 수 있다”고 말했다.

현재 ASML은 빛 입사각과 반사각 간 간섭 등 기술 문제를 해결하고 시제품 생산에 박차를 가하고 있다. 기존 EUV 장비보다 생산성 높은 반도체 웨이퍼를 만들기 위한 기술 구현이 한창이다. 정 상무는 “시제품을 글로벌 반도체연구소인 아이멕과 협업을 통해 만들고 있다”면서 “하이 NA 시스템 통합을 위한 공장 증설도 이뤄지고 있다”고 덧붙였다.

권동준기자 djkwon@etnews.com