삼성전자가 고성능 인공지능(AI) 프로세서와 서버 등에 필요한 '3D 적층 D램' 생산량을 30배 이상으로 늘린다.

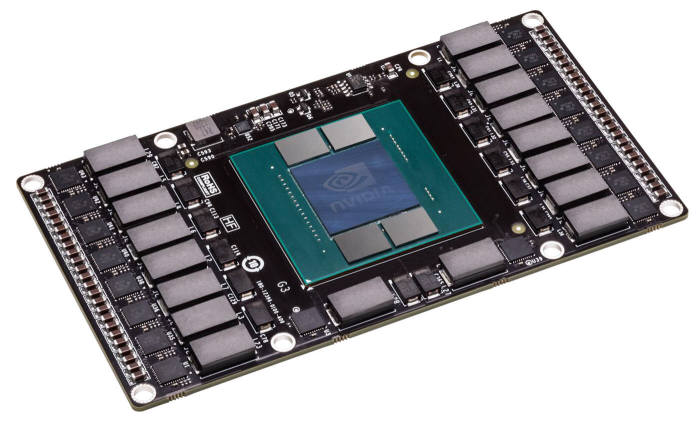

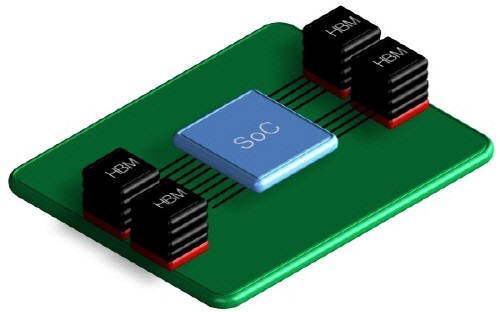

3D D램은 실리콘관통전극(TSV) 공정 기술로, D램 칩을 수직으로 쌓아 생산한다. 입출력(I/O) 대역폭이 늘어나 데이터 전송 속도가 크게 빨라진다. 삼성전자가 생산한 3D 적층 구조 D램은 AI 프로세서 시장 공략에 나선 미국 인텔과 엔비디아에 공급될 전망이다.

30일 업계에 따르면 삼성전자 반도체사업부는 최근 장비 협력 S사에 서멀콤프레션(TC) 본더 20대를 발주했다. TC 본더는 TSV 공정 도입에 필요한 핵심 장비다.

TSV는 칩에 매우 미세한 구멍을 뚫고 동일 칩 여러 개를 수직으로 적층, 구멍 속을 구리로 채워서 전극을 형성하는 첨단 적층 기법이다. TC 본더는 가공을 마친 웨이퍼 위로 구멍이 뚫려 있는 개별 칩을 여러 단으로 쌓는다. 열을 가하고 압착 방식으로 칩을 적층하는 방식이어서 서멀콤프레션(열압착) 본더라는 이름이 붙었다.

새로 도입되는 TC 본더는 본딩 헤드가 8개 달린 혁신 장비다. 기존의 삼성전자 반도체 생산 라인에는 싱글 헤드 장비 5대가 사용됐다. 산술로만 본다면 장비 대당 생산성이 8배 늘어나는 것이다. 헤드 8개를 탑재한 TC 본더 20대면 싱글 헤드 장비 160개를 도입한 효과를 볼 수 있다.

장비 입고 후 가동을 시작하는 올해 말을 기점으로 삼성전자 TSV 적층 공정 생산 용량이 기존 대비 30배(헤드 5개→160개) 이상 늘어나게 된다.

헤드 8개를 탑재한 것은 혁신 기술로 꼽힌다. 헤드를 여러 개 달면 적층 시 정밀도 저하 문제가 야기됐기 때문이다. 그러나 삼성은 협력사와 수년간의 연구개발(R&D) 끝에 상용 생산 라인에 도입할 정도로 성능과 정확도를 개선했다.

삼성전자는 이 공정 라인을 활용해 AI 프로세서에 탑재되는 고대역폭메모리2(HBM2) 생산을 우선 늘리고, 서버용 차세대 메인 메모리인 3차원수직적층(3DS) D램의 출하도 확대한다.

TSV 기술로 정보 입·출구 수를 크게 늘린 HBM2는 현존하는 D램 가운데 가장 빠른 GDDR5와 비교하면 단위 시간당 7~8배 많은 데이터를 주고받을 수 있다. 전력 소모량 역시 적다. HBM2는 머신러닝(기계학습)과 이를 통해 AI를 구현하는 인텔의 제온파이 프로세서, 엔비디아의 최신 그래픽처리장치(GPU) 프로세서에 붙는다.

HBM2가 초고성능 프로세서에 직접 붙는 특수 D램이라면 3DS D램은 동일 적층 방식으로 구현한 서버 모듈용 메인 D램이다. IO 생성용 구멍이 HBM2보다 적지만 일반 비적층형 D램보다는 속도가 빠르고 저전력을 구현한다. 인메모리 데이터베이스(DB)를 구현하는 특수 서버에 탑재될 전망이다. 삼성은 독일 전사자원관리(ERP) 소프트웨어(SW) 업체 SAP와 관련 기술을 개발하고 있다고 발표한 바 있다.

삼성전자는 내년에 증산 투자 효과로 HBM2와 3DS D램을 각각 개별 칩 기준 월 100만개가량 출하한다.

TSV D램 적층 기술은 CMOS이미지센서(CIS)에도 활용된다. 삼성전자는 CIS에 로직 칩과 D램을 동시에 얹는 '3단 적층' 제품을 개발, 양산 준비에 들어갔다. CIS에 D램을 적층하면 데이터를 임시 저장하는 공간이 생겨나 스마트폰 카메라에서 초당 1000장의 사진을 기록하는 '초고속 촬영' 기능을 사용할 수 있게 된다. 애플 아이폰7에 탑재된 '슬로모션'은 초당 120장을 촬영한다. 성능이 약 8배 우수하다.

한주엽 반도체 전문기자 powerusr@etnews.com