이석희 SK하이닉스 사장이 메모리 반도체 기술 미래 비전을 밝혔다. 그는 현재 마주한 해결 과제를 극복하면 10나노 이하 D램, 600단 이상 낸드플래시 제조도 가능할 것이라고 말했다.

이석희 SK하이닉스 사장은 22일 세계적인전기전자공학 학술단체인 전기전자기술자협회(IEEE) 국제신뢰성심포지엄(IRPS) 기조연설자로 나서 이같이 밝혔다.

이 사장은 각 메모리별로 당면한 과제를 꼽았다. D램의 경우 △패터닝 한계 극복 △셀 커패시터 용량 확보 △저(低) 저항 배선 기술 확보 문제를, 낸드플래시의 경우 △고종횡비(HARC) 식각 기술 확보 △셀 유전체 특성 확보 △박막 문제 해결 등을 언급했다.

그는 이를 해결하기 위한 SK하이닉스의 노력과 대안을 제시했다. D램 분야에서는 극자외선(EUV) 기술 도입이 대표적이다.

이 사장은 “안정적인 EUV 패터닝을 위해 각종 소재 및 포토레지스트 개발, 불량 관리 등 생산성 향상에 만전을 기하고 있다”고 전했다. 또 “차량용 반도체처럼 고도의 신뢰성이 요구되는 응용처에는 소프트 에러에 대한 해결책을 찾기 위해 최적화된 공정 기술을 적용하고 있다”고 말했다.

낸드플래시 분야에서는 전하를 효율적으로 저장하고 필요할 때 내보낼 수 있는 셀 특성 향상을 위해 원자층증착(ALD) 기술 도입을 적극적으로 진행하고 있다. 또 박막에 가해지는 기계적 스트레스를 관리하면서 셀 옥사이드/나이트라이드(ON) 물질 최적화도 진행 중이다.

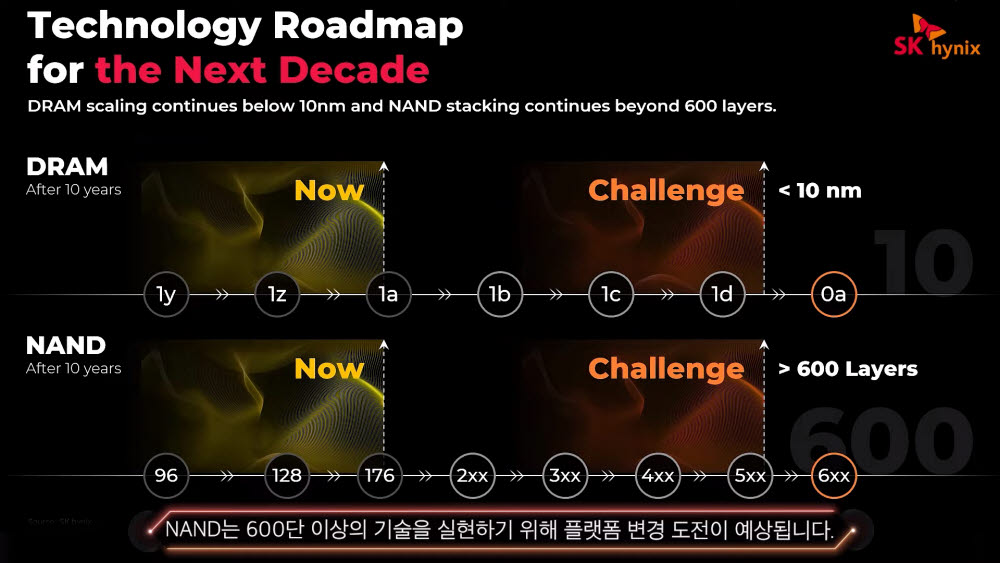

현재 SK하이닉스는 10나노급 4세대(1a) 양산을 준비하고 있고 업계 최고층인 176단 낸드플래시 개발을 완료했다.

이 사장은 “D램과 낸드 각 분야에서 기술 진화를 위해 물질과 설계 구조를 개선하고 있다”며 “성공적인 플랫폼 혁신이 이뤄진다면 10년 뒤 D램에서 10나노(㎚) 이하 공정 진입, 낸드는 600단 이상 적층까지 가능하다”고 전했다.

아울러 협력사들과의 생태계 조성에 적극적으로 나서겠다는 메시지도 전달했다.

그는 “반도체 산업 생태계의 다양한 파트너들이 협력적 동반 관계를 맺어야 한다”며 “고객과 협력사와의 협업을 기반으로 개방적 혁신을 지향할 것”이라고 밝혔다.

강해령기자 kang@etnews.com