인텔은 기술 전략 설명회 '인텔 엑셀러레이티드'에서 반도체 패키징 신기술 로드맵도 공개했다. 반도체 성능 향상에 패키징 기술의 중요성이 커지고 있어 차별화한 패키징 기술을 선보여 시장을 주도하겠다는 포부다.

인텔은 2023년 목표로 독자 패키징 기술인 '포베로스 옴니'와 '포베로스 다이렉트'를 준비하고 있다고 소개했다.

포베로스는 2018년 말 인텔이 공개한 3차원(3D) 적층 방식 패키징 기술이다. 보다 적은 면적을 차지하면서, 신호 지연과 전력 소모를 줄일 수 있어 차세대 패키징 기술로 관심을 모았다.

인텔은 2022년 하반기 생산하는 PC용 '메테오레이크' 프로세서에 포베로스 기술을 적용할 계획이라고 설명했다.

포베로스 옴니와 포베로스 다이렉트는 포베로스를 개선한 기술이다. 반도체 적층 시 실리콘관통전극(TSV)과 구리 기둥을 함께 사용한 것이 특징이다.

TSV는 반도체에 구멍을 뚫어 상단 칩과 하단 칩을 연결하는 기술이다. 데이터 전송 속도 향상에 강점이 있다. 단, 기술 구현이 어렵고 공정 비용이 많이 든다.

이에 인텔은 포베로스 옴니에서 TSV를 쓰지 않아도 되는 부분을 구리 기둥으로 연결해 비용 절감과 전력 효율성 개선을 꾀했다.

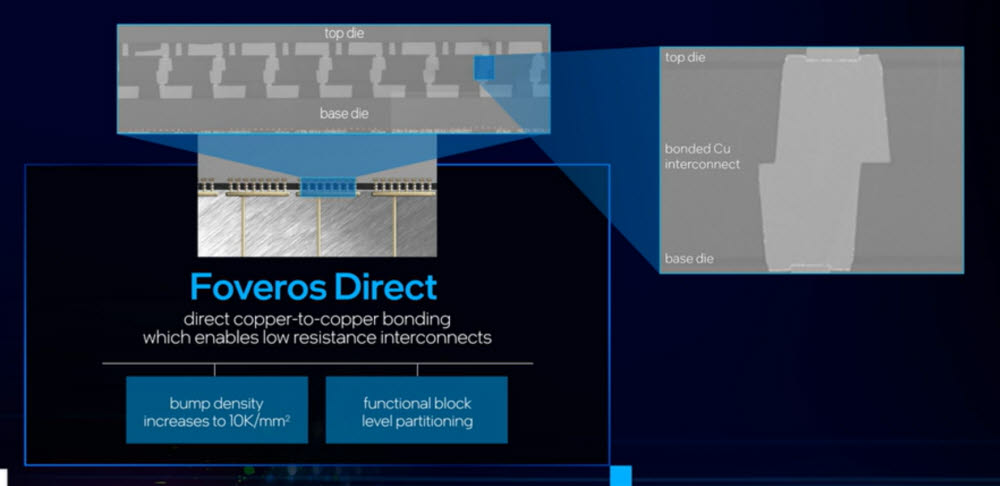

포베로스 다이렉트 역시 구리를 활용한 기술이다. 실리콘을 구리로 직접 연결해 저항을 최소화한다.

기존 연결 방식은 접합면에 첨가 물질이 있지만, 구리로 직접 연결하면 접합 간격을 줄일 수 있다. 접합 간격은 신호 지연과 전력 소모와 밀접한 연관이 있어 간격을 줄일수록 효율이 높아진다.

인텔은 '임베디드 멀티다이 인터커넥트브릿지(EMIB)' 기술도 확대 적용하겠다고 강조했다. EMIB는 반도체(다이)를 연결하는 가교 역할로, 다이 연결 부분 아래에 숨겨 다양한 형태의 반도체 칩을 만들 수 있도록 한다. 기존 패키징 기술과 비교해 대역폭은 2배, 전력 효율성은 4배 높일 수 있다. 내년 생산 예정인 서버용 CPU 사파이어 래피즈에 적용된다.

인텔이 반도체 패키징 기술에 힘을 싣는 건 반도체 제조 과정에서 패키징 기술이 한층 중요해졌기 때문이다. 반도체 성능은 초미세 공정 기술이 한계에 도달하고 기술 극복에 시간이 걸리면서 성능 향상이 점차 힘들어지고 있다. 대신 후공정인 패키징 기술을 통해 성능을 개선하는 방식이 주목받는다.

또 반도체 칩 디자인 관점에서도 패키징 기술 비중이 커지고 있다. 모바일 등 정보기술(IT) 기기가 다양해져 유연한 반도체 디자인을 위해서는 패키징 기술 개선이 선행돼야 한다.

패키징은 인텔이 자신하는 기술이기도 하다. 인텔의 차세대 패키징 기술은 이번에 발표한 고객사 아마존웹서비스의 반도체 생산에 적용될 전망이다.

권동준기자 djkwon@etnews.com