TSMC와 인텔이 반도체 미세화 공정 한계를 뛰어넘는 차세대 패키징 기술에 속도를 내고 있다. 미세화의 기술적 난제를 후공정 기술로 극복하겠다는 것이다.

한국마이크로전자 및 패키징학회(KMEPS)와 전자신문사 공동 주최로 개최된 '국제패키징기술세미나(ISMP) 2022'에서 아므란 에이탄 TSMC 첨단 패키징 기술 서비스(APTS) 이사가 “TSMC 3차원 시스템 온 인터그레이티드칩(SoIC) 중앙처리장치(CPU) 패키징을 양산한 데 이어 반도체 칩사이 간격을 좁히는 하이브리드 본딩 기반 고성능 반도체를 내놓을 것”이라고 밝혔다.

SoIC는 반도체를 쌓는 패키징 기술이다. 반도체 적층 기술에서 여러 반도체를 하나로 붙이는 기술을 말한다. TSMC는 지난 3월 AMD 고성능 컴퓨팅(HPC)용 CPU를 SoIC 적층 패키지 기술로 양산했다. 10배 이상 통신 속도를 높였다. TSMC는 기존 솔더에 마이크로 범프를 하나로 결합한 기술도 개발했다. TSMC는 칩사이 간격을 종전 대비 5분의 1 수준으로 줄여 전기 전도를 올리면서 속도 올리고 에너지 효율을 높인다. 하이브리드 패키지 기술로 고성능 슈퍼컴퓨팅 시장을 공략 속도를 높일 예정이다.

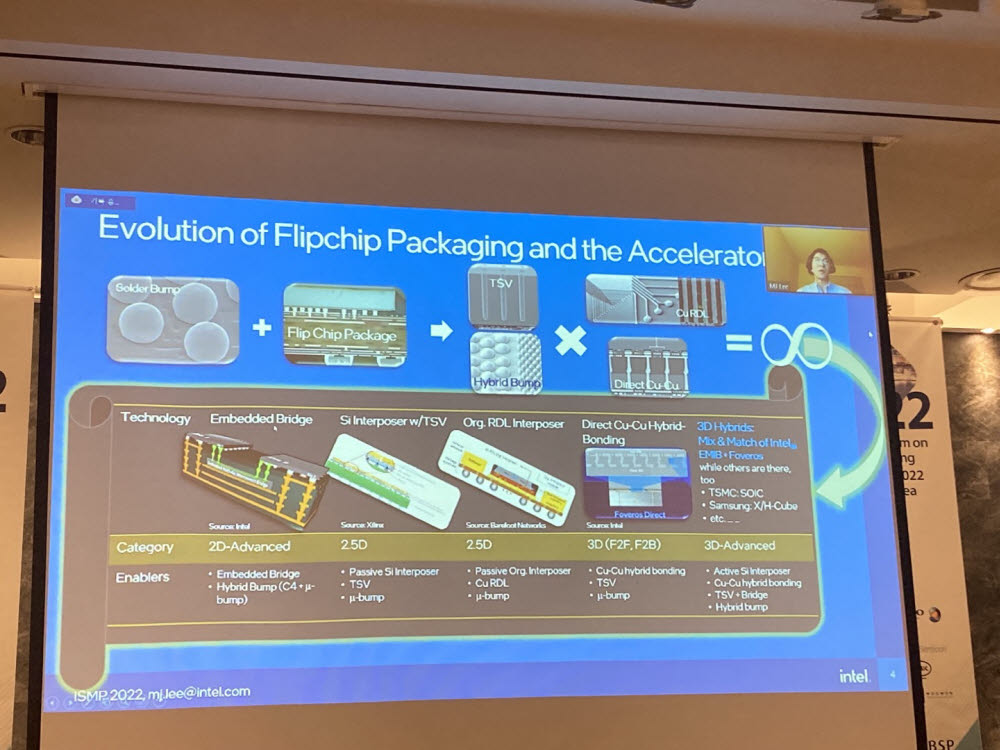

인텔도 3차원 하이브리드 패키징 기술을 공개했다. 칩 사이를 솔더 없이 붙이는 포베로스 다이렉트 본딩은 칩 간격을 최소화한다. 반도체 여러개를 자유롭게 연결해 데이터 처리 속도를 빠르게 하면서도 소모 전력을 줄일 수 있다. 이명준 인텔 이사는 “마이크론 수준으로 반도체 간격을 구현하면서 칩을 최대한 많이 넣고 속도와 성능 개선하기 위해 노력하고 있다”며 “첨단 패키징 기술을 적용한 반도체 제품을 계속 공개할 것”이라고 말했다.

TSMC와 인텔은 첨단 패키징 기술을 활용해 반도체 성능을 개선하면서 데이터 처리 성능을 올릴 수 있기 때문이다. 4~5나노 첨단 반도체를 생산하면서 반도체 성능을 더욱 높일 수 있는 방법으로 데이터 시대에 한계를 극복할 수 있기 때문이다. 메모리 반도체 업체들과 협력해 차세대 고성능 컴퓨터, 인공지능(AI), 데이터센터 등 반도체 수요에 대응하기 위한 기술도 개발한다.

에이탄 이사는 메모리와 로직 반도체의 이종 결합을 위한 협력 사례를 공개했다. 그는 “2023년 하이브리드 본딩 기술을 이용해 데이터 처리 성능을 높일 수 있는 고대역폭 메모리를 지원한다”고 말했다. 이명준 이사도 “고대역폭 메모리를 지원하기 위한 차세대 반도체 패키징 여러 기술을 적용하고 있다”고 강조했다. 글로벌 메모리 시장 침체 속에서 고성능 반도체 시장 수요를 열어줄 수 있을 것으로 기대된다.

김지웅기자 jw0316@etnews.com