인텔이 시스템반도체(로직) 트랜지스터를 수직으로 쌓는 '3D 적층' 신기술을 공개했다. 반도체 미세화 한계를 극복하고 집적도를 대폭 향상시킬 수 있는 3D 적층은 반도체 업계에서 연구개발(R&D) 경쟁이 치열한 기술이다. 인텔은 독자 개발한 신개념 전력공급 기술을 적용해 반도체 3D 적층 차별화에 도전한다. 차세대 반도체 개발을 위한 한판 승부가 예고됐다.

인텔은 10일 국제전자소자학회(IEDM 2023)에서 3D 적층형 트랜지스터 기술 성과를 공개했다. CFET(상보형전계효과 트랜지스터)이라 불리는 이 기술은 반도체 구성 요소인 트랜지스터를 위로 쌓는 3D 구조가 핵심이다. 지금까지 메모리에서 반도체 성능을 끌어올리기 위해 적용해왔던 구조로, 시스템 반도체 트랜지스터에서는 아직 활용된 바가 없다.

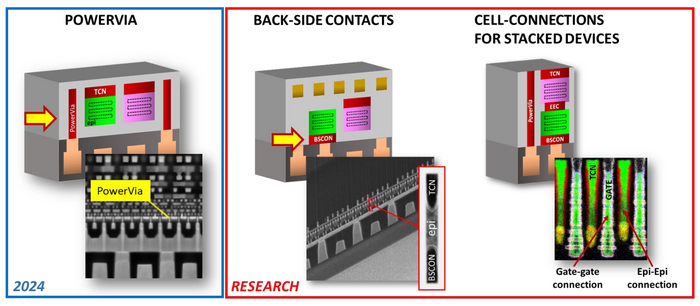

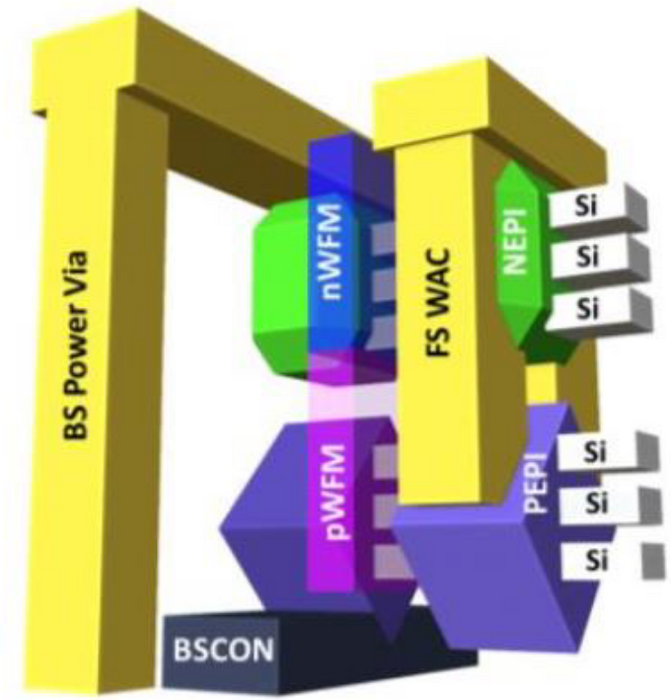

인텔은 “CFET을 수직으로 쌓아 올려 공간 효율성을 크게 높이고 반도체 성능을 향상시킬 수 있다”며 “후면 전력 공급 기술과 후면 접촉 기술을 결합, 인텔의 게이트올어라운드(GAA) 트랜지스터 리더십을 강조했다”고 밝혔다.

반도체 미세화 전환 속도가 늦어지면서 CFET은 반도체 집적도를 높이는 방법으로 주목받고 있다. 트랜지스터를 옆(수평)이 아닌 위로 쌓으면서 반도체 공간 활용도를 개선할 수 있기 때문이다. 한 반도체 칩에 더 많은 트랜지스터를 넣을 수 있다는 의미다. 또 전류 누설 등 셀 간 간섭도 최소화할 수 있다.

이 같은 강점으로 인텔뿐 아니라 삼성전자와 TSMC 등 글로벌 반도체 제조사들이 CFET 개발에 뛰어들었다. 모두 장기 기술 로드맵으로 설정, 기술확보 경쟁이 한창이다.

인텔은 자체 개발한 전력공급 기술로 3D 적층 차별화에 나설 예정이다. IEDM 2023에 함께 공개한 '후면 직접접촉 기술'이 주인공이다. 후면 직접접촉 기술은 인텔이 2024년 양산에 적용할 후면 전력공급 장치(BSPDN)를 개선한 것으로, 반도체 웨이퍼 후면에서 트랜지스터에 직접 배선을 접촉시켜 원활한 전력 공급을 가능하게 한다. 기존 후면 전력공급 장치는 트랜지스터에 직접 전력을 공급하지 않고 별도 배선이 필요해 공간 활용도가 떨어졌다. 인텔은 “금속 층을 줄일 수 있고 동시에 전력 소모를 낮출 수 있다”고 부연했다.

후면전력 공급장치 역시 차세대 반도체 기술로 손꼽히며 주요 반도체 기업 간 경쟁이 치열한 분야다. 삼성전자와 TSMC도 구체적인 양산 적용계획을 밝히지 않았지만 잇따라 연구 성과를 공개하는 등 공격적인 행보를 보이고 있다. 인텔은 독자적인 후면 직접접촉 기술을 앞세워 경쟁 우위를 확보할 방침이다.

인텔은 이날 실리콘 트랜지스터와 질화갈륨(GaN) 트랜지스터를 통합한 300밀리미터(㎜) 웨이퍼도 소개했다. 'GaN 온 실리콘'이라 불리는 기술로, 전력 반도체에서 많이 활용된다. 인텔은 “실리콘과 GaN의 공정 통합으로 기술적 진전을 달성했으며, 전력공급을 위한 고성능의 대규모 직접 회로 솔루션인 'DrGaN'을 성공적으로 시연했다”며 “미래 컴퓨팅의 높은 전력밀도와 효율성 요구사항에 맞춰 전력공급 솔루션을 구현할 잠재력을 확보했다”고 밝혔다.

권동준 기자 djkwon@etnews.com