삼성전자가 급증하는 인공지능(AI) 반도체 수요에 대응하기 위해 파운드리, 메모리, 패키징을 일괄 제공하는 AI 통합 솔루션 전략을 추진하겠다고 밝혔다.

삼성전자는 12일(현지시간) 미국 실리콘밸리에서 'AI 혁신 강화(Empowering the AI Revolution)'를 주제로 파운드리 포럼을 개최하고 이같은 기술 전략을 밝혔다.

최시영 삼성전자 파운드리사업부 사장은 “AI를 중심으로 모든 기술이 혁명적으로 변하는 시점에서 가장 중요한 건 AI 구현을 가능하게 하는 고성능·저전력 반도체”라며 “'게이트 올 어라운드(GAA) 공정 기술과 광학 소자 기술 등을 통해 AI 시대에 고객들이 필요로 하는 원스톱(One-Stop) AI 솔루션을 제공할 것”이라고 말했다.

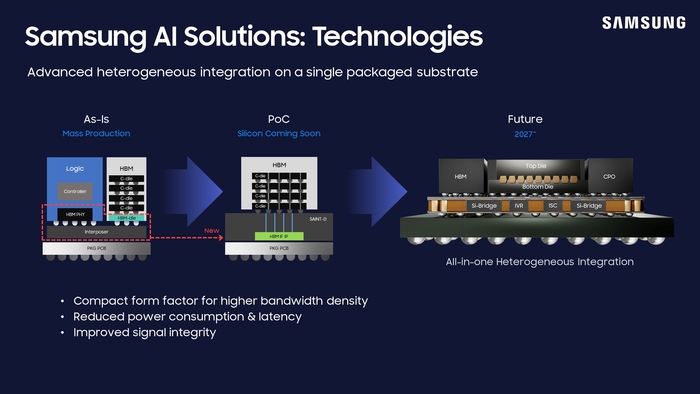

통합 AI 솔루션은 AI 반도체 제조에 필요한 기술과 서비스들을 삼성이 일괄 지원하겠다는 것이다. 파운드리와 메모리, 패키징 사업을 보유하고 있는 만큼 AI 반도체에서 요구하는 고대역폭메모리(HBM)나 첨단 하이브리드패키징을 제공해 반도체 사업을 확대하겠다는 전략이다. 삼성전자는 통합 AI 솔루션을 활용할 경우 파운드리, 메모리, 패키지 업체를 각각 사용할 경우 대비 칩 개발부터 생산에 걸리는 시간을 약 20% 단축할 수 있다고 강조했다.

삼성은 이날 다변화하는 반도체 수요에 대응, 신기술도 제공하겠다고 밝혔다.

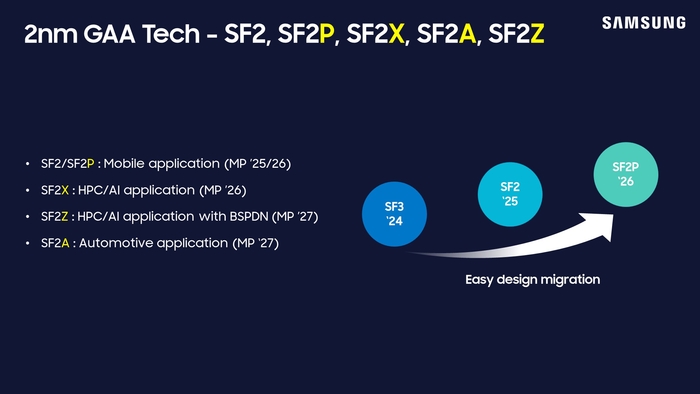

우선 기존 파운드리 공정 로드맵에 2㎚(SF2Z), 4㎚(SF4U) 신공정을 더했다. SF2Z 공정은 후면전력공급기술(BSPDN) 기술을 포함하며 2027년까지 기술 개발을 완료할 계획이라고 밝혔다. 광학적 축소로 회로 선폭을 줄여 기존 4㎚ 공정 대비 성능·전력·크기(PPA)를 개선한 SF4U는 2025년 양산할 예정이다.

BSPDN은 전류 배선층을 웨이퍼 후면에 배치해 전력과 신호 라인의 병목 현상을 개선하는 기술이다. 반도체 회로 미세화로 전류 배선층을 전면에 함께 새기기 어려웠는데 이를 후면으로 옮기면 전력 효율과 성능을 개선할 수 있다.

삼성전자는 SF2Z가 기존 2㎚ 공정 대비 성능·전력·크기(PPA)를 개선하고, 전류의 흐름을 불안정하게 하는 '전압강하' 현상을 대폭 줄여 고성능 컴퓨팅 설계 성능을 향상시킬 수 있다고 강조했다.

기존 로드맵과 관련해서 올해 하반기 GAA 기술 기반 2세대 3㎚ 공정 양산을 시작하고, 1.4㎚ 공정 양산 목표 시점은 기존과 같은 2027년을 유지한다고 발표했다. 1.4㎚ 공정 양산 계획에 맞춰 목표한 성능과 수율을 확보해가고 있다고 덧붙였다.

또 2027년까지 광학 입출력(I/O) 구현을 위한 실리콘 포토닉스 기술 개발을 완료할 계획이다. 이는 반도체 신호 전달 방식을 기존 전기에서 광자로 바꾸는 기술이다. 데이터 전송 속도, 전력 효율성을 큰 폭으로 개선할 수 있어 AI 반도체에 필요한 기술로 꼽힌다.

삼성전자는 급성장하는 AI 분야 고객 협력을 강화할 방침이다. 올해 AI 수주 규모는 지난해 대비 80% 이상 성장했다고 전했다. 또 8인치 파운드리와 성숙공정에서도 PPA와 가격경쟁력을 개선한 공정 포트폴리오로 다양한 고객 요구에 대응한다.

삼성전자는 13일(현지시간) '삼성 어드밴스드 파운드리 에코시스템(SAFE) 포럼 2024'를 개최한다. 파트너사들과 AI 시대 고객 맞춤형 기술과 솔루션을 함께 공유하게 제시한다. 지난해 출범한 첨단 패키지 협의체 'MDI(Multi-Die Integration) 얼라이언스'의 첫 워크숍도 진행한다. 2.5D와 3D 반도체 설계에 대한 종합적인 솔루션을 구체화할 예정이다.

박진형 기자 jin@etnews.com