삼성전자가 차세대 트랜지스터 구조인 '게이트올어라운드(GAA)'를 적용한 2나노 반도체 공정을 2025년부터 양산한다. TSMC와 인텔보다 1년여 늦은 일정이지만, 3나노 공정에 우선 적용해 얻은 양산 기술을 활용해 수율을 확보한다는 전략이다. 삼성이 2나노 공정 양산 계획을 구체화한 것은 이번이 처음이다.

삼성전자는 6일(미국 현지시간) 온라인으로 개최한 '삼성 파운드리 포럼 2021'에서 2025년 GAA 기반 2나노 공정 양산을 시작할 것이라고 밝혔다. 앞서 내년 상반기 3나노 공정에 GAA 기술을 최초 도입하고, 2세대 GAA 기반 3나노 공정은 2023년부터 양산한다. 최시영 삼성전자 파운드리사업부 사장은 “GAA 등 첨단 미세공정뿐 아니라 기존 공정에서도 차별화된 기술 혁신을 이어갈 것”이라고 말했다.

삼성전자의 2나노 공정 양산 일정은 TSMC와 인텔보다 1년여 뒤진다. 하지만 TSMC와 인텔은 2나노 공정에 처음 GAA를 도입할 예정이어서 기술 안정성과 수율에서는 삼성전자가 우위를 차지할 수 있다. 2나노 공정에 도입할 GAA는 3세대 기술이다. 삼성전자는 3나노 공정도 안정적 생산 수율을 확보하며 양산을 위한 준비가 이뤄지고 있다고 밝혔다.

삼성전자는 포럼에서 핀펫 기반 17나노 신공정도 발표했다. 17나노 공정은 28나노 공정 대비 성능은 39%, 전력 효율은 49% 향상될 것으로 기대된다. 반도체 면적은 43% 줄어들 것으로 보인다. 삼성전자는 28나노 공정을 주로 활용했던 이미지센서, 모바일 디스플레이구동칩 등에 17나노 신공정을 적용할 수 있는 만큼 응용처 확대를 기대했다.

삼성 파운드리 포럼 2021은 역대 파운드리 포럼 중 가장 많은 500개사, 2000명 이상 팹리스 고객과 파트너가 참석했다. 삼성전자는 파운드리 생태계를 위한 '세이프 포럼'을 11월 온라인으로 개최한다.

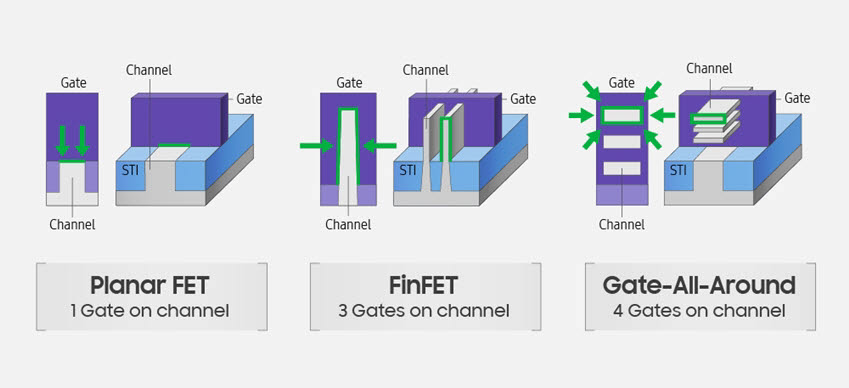

<용어설명> GAA는 반도체 트랜지스터 구조 대세인 핀펫의 한계를 극복한 기술이다. 반도체 내 전류를 제어하는 게이트와 채널 접합면을 기존 3면에서 4면으로 늘려 보다 세밀한 전류 제어가 가능하다. 3나노 이하 공정에서는 핀펫보다 GAA가 더 효율적인 것으로 알려졌다.

<삼성전자·TSMC·인텔 미세 공정 및 트랜지스터 구조 전망>

자료=업계 취합(인텔은 새로운 공정 단위인 '옹스트롬'을 사용, 타사와 나노 단위 비교가 정확하지 않음)

권동준기자 djkwon@etnews.com