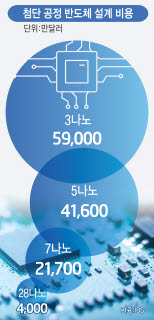

관련 통계자료 다운로드 첨단 공정 반도체 설계 비용

관련 통계자료 다운로드 첨단 공정 반도체 설계 비용

3나노미터 이하 첨단 공정 반도체 설계 비용이 최대 7200억원에 이르는 것으로 나타났다. 중소 팹리스와 스타트업이 대규모 투자를 유치하지 못하면 사실상 진입이 어려운 셈이다. 인공지능(AI) 등 차세대 반도체 시장이 막강한 자본력을 앞세운 소수 기업 중심으로 재편될 것이라는 우려가 나온다.

시장조사업체 IBS에 따르면 3나노 공정을 활용하는 반도체 디자인(설계) 비용은 최대 5억9000만달러(약 7200억원)에 육박하는 것으로 나타났다. 5나노(4억1600만달러)와 7나노(2억1700만달러) 공정 설계 비용과 견줘 각각 41.8%, 171.8% 증가한 수치다. 현재 28나노 공정 설계 비용이 4000만달러 수준인 것을 고려하면 3나노 공정은 10배 이상의 자금이 필요하다.

IBS 조사가 최대 설계 비용을 반영, 현장에서 실제 투입되는 비용과 차이는 있다. 그러나 초미세 공정으로 갈수록 비용이 급등하는 건 사실이다. 반도체 디자인하우스(설계 지원) 관계자는 “설계자산(IP)부터 설계자동화(EDA), 시제품 개발을 위한 공정 비용 전체가 급등하는 구조”라며 “한 자릿수 나노 공정을 활용한 설계는 수백억원에서 수천억원까지 증가하는 추세”라고 밝혔다.

설계 비용 급등은 소프트웨어(SW)와 반도체 설계자산(IP) 비용 증가 때문이다. 반도체 초기 설계 비용의 절반을 차지하는 항목이다. 초미세 공정으로 갈수록 반도체 설계에 투입되는 인력이 급격히 늘어나는데 이에 따라 반도체 SW 라이선스 비용도 크게 뛸 수밖에 없다. 업계에 따르면 5나노 이하 반도체 설계에는 100명 이상의 인력이 필요한 것으로 알려졌다. EDA 툴 등 활용하는 SW 카피 라이선스 절대 수가 늘 수밖에 없다. 한 중소 팹리스 관계자는 “3나노 반도체 IP도 해외 일부 기업이 독점하고 있어 부르는 것이 값”이라며 “가격 협상력이 약한 중소 팹리스는 울며 겨자 먹기 식으로 높은 IP 비용을 지불할 수밖에 없다”고 밝혔다.

현재 3나노 반도체 설계가 가능한 업체로는 삼성전자, 퀄컴, 애플, 엔비디아, AMD 등이 회자된다. 모두 글로벌 반도체 기업으로, 자본력이 막강하다. 이들은 반도체 SW 기업과의 가격 협상력도 뛰어나다.

협상력이 약한 중소 팹리스나 스타트업에 3나노 진입은 '그림의 떡'이다. 퓨리오사AI, 리벨리온 등 일부 국내 반도체 스타트업만 5~14나노 공정으로 반도체 칩을 개발 중이다. 이들은 모두 수백억원 규모의 투자 유치에 성공했지만 차세대 반도체 설계를 위해서는 추가 투자가 필요하다.

시제품 개발 비용도 중소 팹리스의 발목을 잡는다. 반도체 설계 후 웨이퍼에 실제 회로를 그려 보는 '멀티웨이퍼프로젝트'(MPW) 비용도 만만치 않기 때문이다. 현재 최선단 공정의 MPW(IP 비용 포함)는 20억~40억원 수준으로 알려졌다.

이 때문에 AI 반도체라 불리는 신경망처리장치(NPU), 지능형처리장치(IPU) 등에 중소 팹리스의 진출은 사실상 불가능하다. 모두 초미세 공정으로 개발해야 하지만 막대한 초기 설계 비용을 감당할 수 없다.

시스템반도체설계지원센터 관계자는 “비용 문제로 국내에 14나노 이하 반도체 팹리스는 손에 꼽힐 정도로 몇 안 된다”면서 “대규모 투자에 성공하든지 IP와 EDA 툴 등 SW 비용을 지원받는 것 외엔 방법이 없다”고 밝혔다.

<첨단 공정 반도체 설계 비용>

자료 : IBS

권동준기자 djkwon@etnews.com