인텔이 트랜지스터 탄생 75주년을 맞아 반도체 집적도와 성능을 대폭 높일 수 있는 신기술을 대거 공개했다. 2년마다 반도체 칩 집적도가 2배씩 증가한다는 '무어의 법칙'을 가속화할 핵심 기술이다. 인텔은 향후 자사 반도체 칩 개발에 신기술을 적용한다.

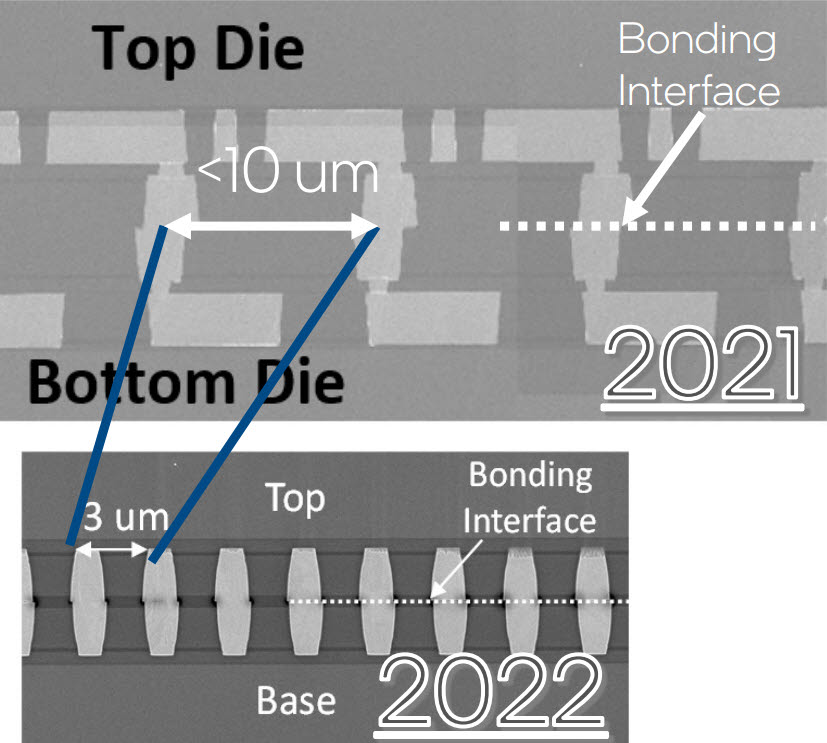

인텔은 4일 국제반도체소자학회(IEDM)에서 '차세대 3차원(3D) 패키징을 위한 준(準) 모놀로식 칩' 기술을 공개했다. 모놀로식은 반도체 각종 기능을 하나의 칩으로 구현한 것으로 초미세 공정 한계로 성능 고도화에 어려움을 겪고 있다. 대안으로 여러 칩(다이)을 하나의 패키지에 담는 '칩렛' 등 각종 차세대 3D 패키징 기술이 주목받고 있다. 다만 이종 칩 간 결합 시 발생하는 집적도 문제는 업계가 풀어야 할 과제다. 이종 칩을 붙일 때 접합 부분 간격이 넓어 반도체 패키지 집적도를 높이는 데 한계가 있기 때문이다. 반도체 패키지 크기가 커지고 성능이 저하되는 원인이 될 수 있다.

인텔은 새로운 소재와 신공정으로 접합부 간격을 3마이크로미터(㎛)까지 줄이는 데 성공했다. 지난해 발표한 10㎛ 대비 3배 이상 간격을 줄였다. 인텔은 “기존(10㎛) 대비 반도체 패키지 집적도를 10배 이상 높일 수 있다”며 “해당 기술을 활용하면 칩렛 크기를 줄일 뿐 아니라 원하는 위치에 반도체 다이를 배치할 수 있을 것”이라고 전망했다. '준 모놀로식'은 기존 칩과 새로운 패키지의 집적도 차이가 거의 없다는 것을 강조하기 위한 이름이다.

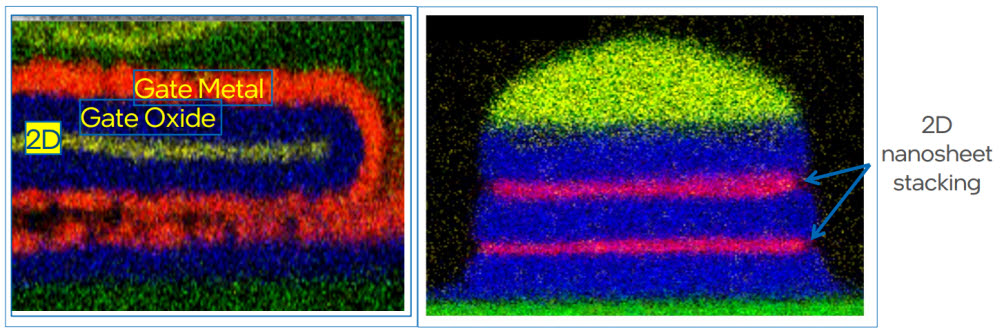

새로운 소재 구조를 활용, 반도체 집적도를 높이고 누설 전류를 효과적으로 통제할 수 있는 기술도 공개했다. 바로 2차원(2D) 구조 소재다. 인텔이 개발한 2D 소재는 기존 3D 구조 소재보다 얇다. 원자 3개 크기로 트랜지스터 구성요소를 만들 수 있어 높은 집적도를 구현한다. 인텔은 차세대 트랜지스터 구조이자 삼성전자가 세계 최초로 양산해 이름을 알린 '게이트올어라운드(GAA)'에서 2D 소재 구조가 빛을 발할 것으로 내다봤다. 반도체 트랜지스터가 작동할 때 흘러나오는 전류를 최소화해 에너지 효율이 높은 칩을 만들 수 있을 것으로 기대했다.

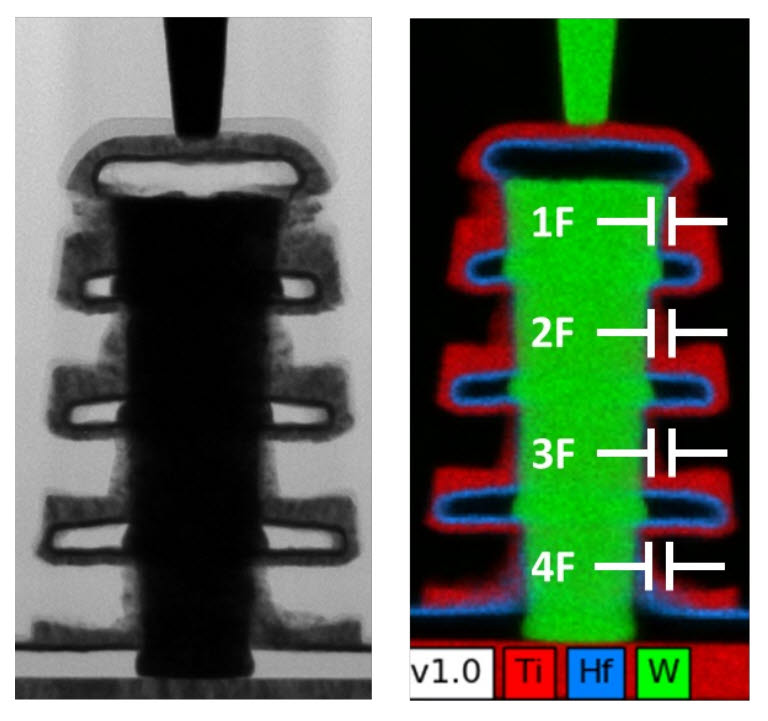

새로운 개념의 비휘발성 메모리 기술도 시연했다. '강유전체메모리(Fe램)'가 주인공이다. Fe램은 기존 D램의 대용량 저장 능력, S램의 속도, 데이터가 지워지지 않는 플래시 메모리 특성을 모두 갖춘 차세대 반도체로 손꼽힌다. 다만 메모리 전하를 저장해 0 또는 1 데이터를 기록하는 캐퍼시터 집적도를 높이는 데 한계가 있었다. 인텔은 2020년 IEDM에서 3D 형태로 캐퍼시터를 적층하는 새로운 개념을 제안한 바 있다. 이번 학회에서 실제 3D 적층 캐퍼시터 기반 Fe램을 시연, 기술 효과를 입증했다. 3D Fe램을 시연한 것은 인텔이 최초다.

인텔은 전력 효율성과 성능을 높인 질화갈륨-실리콘 기술과 적은 구동전압으로 반도체 칩을 제어할 수 있는 기술도 선보였다. 인텔은 “(해당 기술을)당장 상용화는 어렵지만 무어의 법칙을 지속적으로 이끌어 갈 계기가 될 것”이라며 “향후 인텔 기술 로드맵에 따라 신기술을 적극 적용해 나갈 방침”이라고 밝혔다.

◇용어설명

트랜지스터=전압 제어로 전류 흐름과 세기를 조절하는 스위치·증폭기 역할을 담당한다. 1947년 미국 벨연구소 윌터 브래튼, 윌리엄 쇼클리, 존 바딘이 처음 개발했다. 집적회로(IC)는 회로 형태로 트랜지스터를 구현, 다양한 기능을 반도체 칩에 담고 있다. 최근 출시되는 첨단 칩에는 트랜지스터가 100억개 가량 내장됐다. 이를 두고 인텔 창립자 고든 무어는 2년마다 반도체 칩 내 트랜지스터 집적도(수)가 두배씩 늘어난다는 경험칙을 발표, '무어의 법칙'으로 유명해졌다. 최근에는 반도체 초미세 공정 한계로 무어의 법칙이 한계에 직면했다는 목소리가 나온다. 반도체 업계에서는 무어의 법칙을 지속 유지하기 위해 총력을 기울이고 있다.

권동준기자 djkwon@etnews.com